- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Muliple USRP RIO 2943R, synchronization and phase lock problem

Solved!07-21-2016 10:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

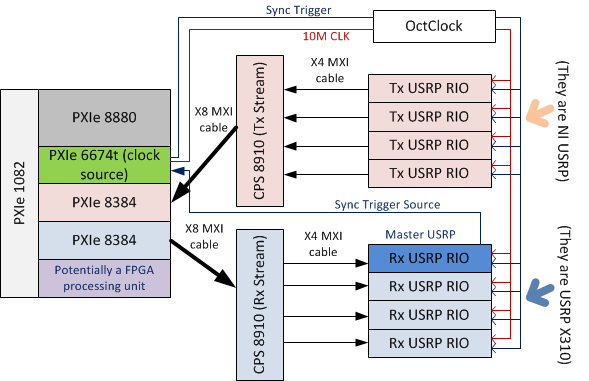

I am using 8 USRP RIO 2943Rs for signal transmitting and receving (4 for Tx and 4 for Rx). I am using the "signal-based" method for synchronizing all the devices. And I have done this. I tested the system the result is very interesting:

1. when I set the IQ sampling rate below 40MS/s, I can obversve very good phase locked Tx and Rx signals (I am using a CW sine wave for testing), please refere to attached video (40MSs locked)

2. BUT, when I set the IQ sampling rate over 60MS/s, I will lose the phase lock. please refere to 60MSs unlocked. My target is to run the system at 120MS/s

I am doubt about whether the problem comes two sides:

a. The synchronization methed is not right

b. OR, do I need to increase the clock which drives the "Streaming Transceiver Engine" loop in FPGA VI. as shown in following picture.

I would like ask experts in forum to discuss the solution of this problem.

Some more information about my system setting:

Solved! Go to Solution.

07-21-2016 10:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here are the video for the above post

07-21-2016 12:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Which model of the 2943R are you using? There are two, based on RF bandwidth. One is 40 MHz, and one is 120 MHz. Which one are you using?

http://sine.ni.com/nips/cds/view/p/lang/en/nid/213002

If you are using the 40 MHz BW USRPs, you should use the 120 MS/s USRP LV FPGA target. If you are using the 120 MHz BW USRPs, you should use the 200 MS/s USRP LV FPGA targets.

Do not use the "USRP X310" target, as this is a legacy/deprecated target. The X310 will work with the other two LV FPGA targets.

07-21-2016 12:33 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brooks,

Thanks for the reply. I should describe this in the post.

I am using 120M USRP 2943R, also I am using 200MS/s FPGA bitfile , the name is called niUSRPRio200_XcvrPps.lvbitx.

BTW, what you mean by "The X310 will work with the other two LV FPGA targets."?

Cheers,

Bo

07-21-2016 12:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@True_Boombo wrote:

What you mean by "The X310 will work with the other two LV FPGA targets."?

The Ettus X310 is supported by the USRP RIO LV FPGA too.

I'll take a look at your videos and see if there's anything I can think of. One thing to note is that the LOs are not synchronized, so there will always be a non-deterministic LO phase offset between different channels on each LO tuning.

07-21-2016 01:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In both videos, the received signals appear to have a constant phase offset with eachother. The 60 MS/s video shows the waveform moving around for acquisition to acquisition, which implies that the Tx and Rx are not starting at the same time. From what I can tell, you do not have a phase lock problem.

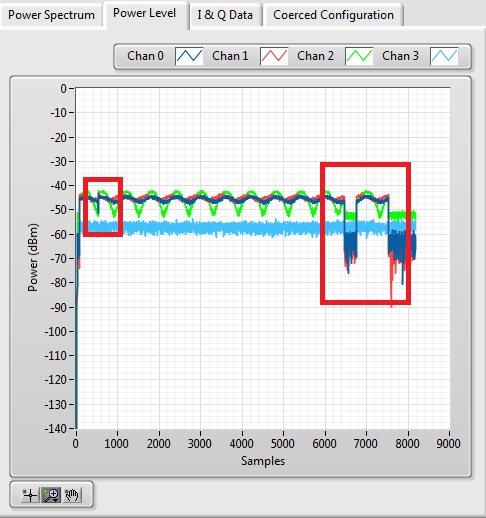

In the 60 MS/s video, it looked like there were moments of discontinuity. Does the power level graph have any dips in it? Do those dips move around?

07-21-2016 01:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brooks,

I took a screen shot of power level graph when the signals are not normal. I guess the parts in the red rectangular are the dips you said.

I think your observation is very interesting. It seems like the phase is still locked, but either Txs or Rxs are not sending or receiving the burst right time. I actually, the higher sampling rate I use, the serverer situation I can observe.

Cheers,

Bo

07-21-2016 01:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@True_Boombo wrote:

I think your observation is very interesting. It seems like the phase is still locked, but either Txs or Rxs are not sending or receiving the burst right time. I actually, the higher sampling rate I use, the serverer situation I can observe.

Yeah, I think the trigger may be the cause. Configuring start triggers across multiple devices doing both Rx and Tx can be difficult. Can you show your host code for configuring the start triggers? Is it one host VI for all 8 USRPs, or are there multiple host VIs?

07-21-2016 02:10 PM - edited 07-21-2016 02:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brooks,

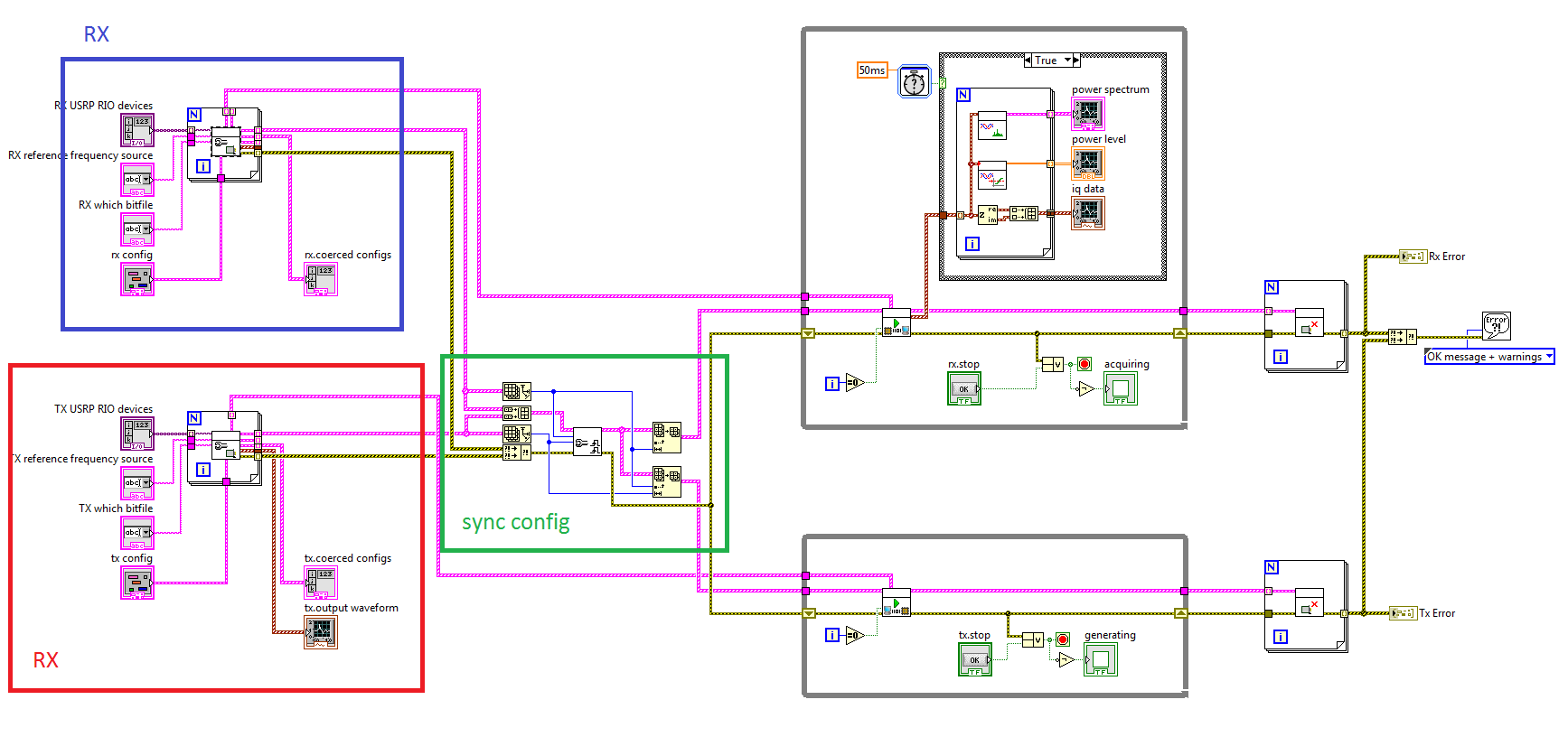

Yep, I have one host VI to configure all 8 USRP RIOs.

As NI does not provide the reference design for synchronize multiple Tx and Rx USRPs together in trigger based multiple device synchronization simple stream example project. I made my own configuration chain in the VI with help from NI support engineers.

The main idea is like this:

1. To create separate Tx devices and Rx devices by using "open and configure device.vi" in the for loop

2. I made some obvious change on the synchronization configuration. (I cascade the Tx session and Rx session handle before the configure the synchronization, in order to make the system recognize the master USRP for generating the sync trigger)

These two step can be seen in following picture.

There are more modifications inside the of the sync configuration sub VI in green box, shown in following picture:

Cheers,

Bo

07-21-2016 02:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I think it is better just attached the modified "configure synchronization.vi" subvi here.