- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How can I get the CLK OUT using PLL on NI PXI-6652?

Solved!10-04-2010 11:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am try to get the CLK OUT using the source CLK from internal either DDS or PXI_CLK10_IN and PLL to the required frequency. In other words I want the CLK OUT coming from the NI PXI-6652 to be PLL to required frequency.

Ashok

Solved! Go to Solution.

10-05-2010 03:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ashok,

What frequency are you trying to PLL to? Do you have a second signal which you want to PLL your CLK OUT with? If you generate the DDS Clock on board then it will be generated at your chosen frequency, and PXI_CLK10_IN is a 10MHz chassis controlled signal you can override with the 6652 card.

National Instruments

Senior Applications Engineer

10-06-2010 10:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am trying to PLL 8.192 MHz clock. Yes, I have generated the clock from DDS at chosen frequency. But instead of routing to CLK OUT can I route to PXI_CLK10_IN?

10-06-2010 12:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

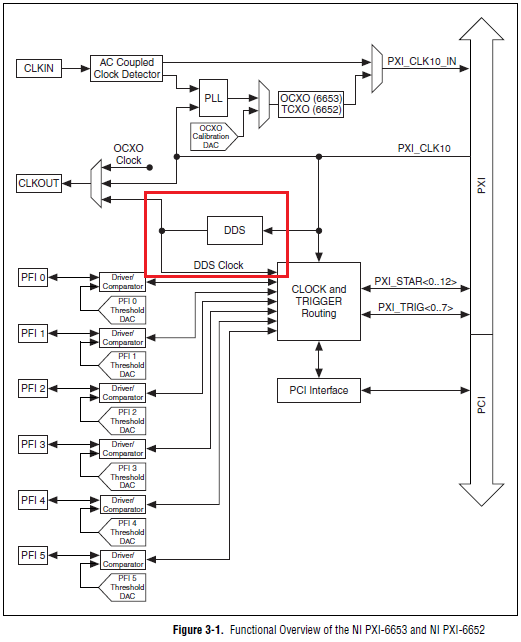

Unfortunately, there is no direct route in hardware to get the DDS clock to PXI_CLK10_IN. Typically, PLL is used for external signals which are out of phase with the system, and not for internally generated signals. Coming from the 665X User Manual online, here is a functional overview of the board:

National Instruments

Senior Applications Engineer

10-06-2010 12:30 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I agree that just confirming. So I decided to route the generated DDS clock at chosen frequency to CLK OUT.