- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

cRIO FPGA with NI 9853 card failing to queue?

Solved!02-21-2017 03:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi.

We're communicating with a transmission over the CAN bus, and having some sort of timing issue. I get messages consistently from the transmission, so I'm not doing something totally wrong, but there is a specific message type that I only get every 2 minutes (roughly), 40 at a time. The transmission is sending this "special" message every ~100mSec or so (I think), and standard messages more frequently. This has been verified using other software (so we know the communication issue isn't on the transmission side).

The baud rate is correct, and there is no way that the transmission is sending more information than the 9853 CAN card can handle.

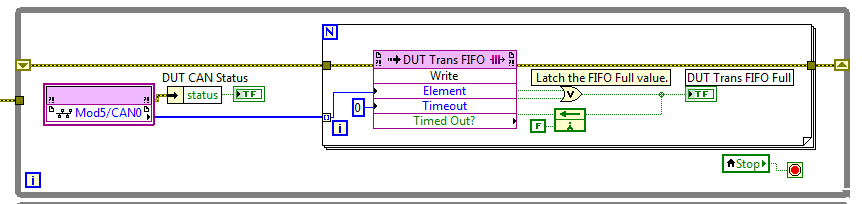

This is the code I have on the FPGA side.

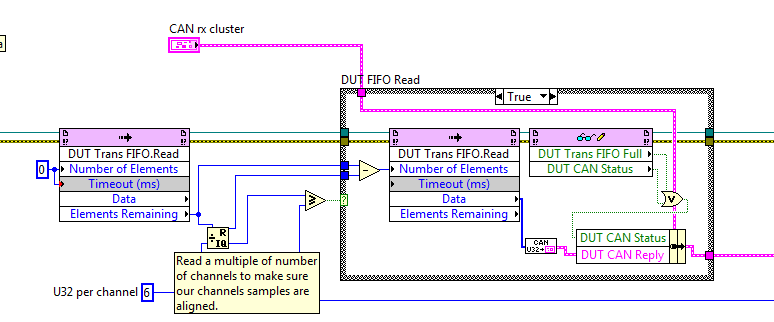

And this is the code I have on the host side, running every 50mSec.

I mostly followed the example code. I did try to read the incoming CAN values as a front panel read of the cluster instead, and had the same issue. The queue works a little better, actually.

The queue is not filling up, and I have not had any indication that I'm failing to acknowledge CAN packets.

Am I doing anything glaringly wrong that could somehow slow down my queuing? Or is there a completely different method I should try to do this correctly? Is my de-queuing the issue?

Please advise?

Solved! Go to Solution.

02-22-2017 03:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

By queuing are you referring to your DUT Trans FIFO? Are you ever seeing DUT Trans FIFO Full go true? If you aren't then your FIFO should be lossless and the issue isn't there.

You might want to try pipelining your CAN0 array. That is, insert a shift register between your CAN0 array and the For loop.

02-27-2017 10:13 AM - edited 02-27-2017 10:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

No, I'm not seeing the FIFO Full go true. You were right in that this wasn't a FIFO issue.

After more fiddling, it turns out I was handling the data wrong after de-queuing. Essentially I was treating what I read in as one packet, instead of multiple. What I have in the case structure would take just one packet, who knows which one (first out of the queue? Last? Random one in the middle?) and pass that out, instead of all of them.

I fixed it by taking the Data wire and running that through a FOR loop instead.

It seems like such a simple problem, now that I've realized my mistake, and I should have seen it much sooner. ![]()

I've also come to realize that there is probably an easier way to handle this, with the actual CAN toolbox. But this works as a brute force method, I suppose.

Thank you, nanocyte, for trying to help.