- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

Spikes in data when FIFO buffer is reduced

10-23-2014 11:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

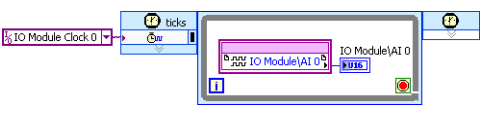

The Sample Clock is a clock exported by the CLIP and you'll need to place the AI node inside of a SCTL that uses that clock. However, the Sample Clock is only available in the most recent version of the NI FlexRIO driver.

If you are using an older version of the driver then you will need to use the IOModClock to drive the SCTL that the AI node resides in. See the image I attached in my last post to see which version requires which clock. If you are using an older version, then I recommend going through the 5733 user guide for information on how to setup the IOModClock.

10-24-2014 07:21 PM - edited 10-24-2014 07:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

David-A,

Thanks for the help. Everything is working properly now.

10-31-2014 12:28 PM - edited 10-31-2014 12:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

David,

As I said previously everything seems to work fine. However, it looks like I cannot have as much logical operations as I had in the SCTL when I was using the 40 Mhz Onboard clock. For example, when I was using the onboard clock I was able to have 3 addition, 3 multiplication operators along with 3 DMO FIFO objects, but when I changed the clock to IOModClock (40 Mhz), all I can have in the loop are 3 multiplication and 2 addition operators. Inserting additonal objects lead to timing violation. Is this expected? If so, what is the difference between the onboard clock and the IOModClock? Thanks for you time.

P. S. I am pipelining to optimize the fpga VI

10-31-2014 01:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Can you start a new thread? The issue you are seeing is unrelated to the OP.

- « Previous

-

- 1

- 2

- Next »