- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Ni 6587 External clock in (single ended - SMA)

Solved!03-12-2015 01:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a PXI 7962R fpga and ni 6587 adapter module. I want to use external clock to implement a simple adder xilinx Ip core. I input the IO clock 0 an external clock of 20 MHz with 3 V pk to pk. I then attached it to single cycle timed loop and fpga clock enable VI and implemented my IP core inside the loop. I did not use the fpga disable vi since i want continuous running vi.

now the project complied but on place and route i didnt see any other clock except for the main 40 MHz implemented. Upon completion of compilation i received an error that fpga and host could not communicate. either the clock z not connected or is nott generated according to specifications. what might be the problem?

Solved! Go to Solution.

03-13-2015 05:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Can you upload your project? I want to check if you added IOModClock0 to the FPGA target and then used that as your clock source for your single cycle timed loop.

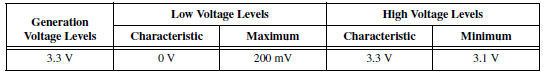

Assuming you've done that correctly, I'm curious what the voltage levels of your clock are. In the spec sheet it states that the minimum high voltage level is 3.1V. Have you checked to make sure that your clock is above 3.1V for high voltage and then below 200mv for low voltage?

03-13-2015 06:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have you consdered the information in this KnowledgeBase Article?

http://digital.ni.com/public.nsf/allkb/A874300E075997D886257AE9006281A0

03-17-2015 04:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here are my attachements for the project. Please identify the problem.

03-17-2015 04:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have verified the voltage levels they r correct. During compilation, I don't see the IO clock 0 implemented on FPGA. There is only the base clock implemented of 40MHz.

03-17-2015 04:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Kindly send me the link of simple project if available on NI forum to check external clock in and PFI 0 signal of NI 6587 adapter module.

03-17-2015 01:31 PM - edited 03-17-2015 01:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The project you attached didnt have the FPGA vi included in it so I'm unable to tell if you were using the IOModClipClock0 properly.

Anyway, attached is a project that has the IOModClipClock0 added to the target, and an FPGA VI that uses it to run some logic in a single cycle timed loop.

03-10-2016 07:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator