- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

HP Loop duration always increases with 2 FPGA on cRIO 9082RT

09-19-2013 01:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

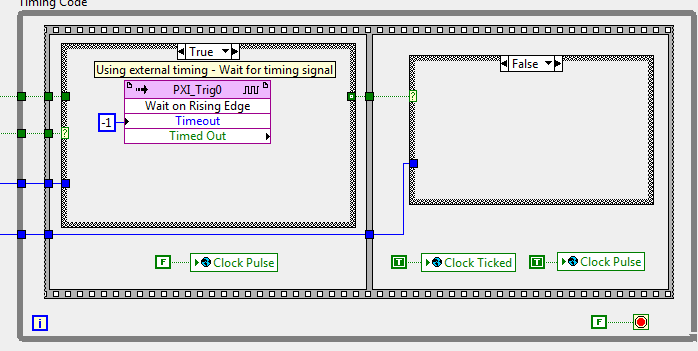

also, in your "Clock_read.PNG" you have the right side of the VI showing reading the voltage... that is wrong. it should set the voltage on the left side (like you are) and do nothing in the right side.

See:

Change that and use FXP constants instead of integers and it should work

09-20-2013 01:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I have already tried to replace cast by constant but it has no effects.

And I think I am obvious put the right side of my "READ_CLOCK.png" to detect the lower edge of the clock.

If I don't put this part, it could be believe detecting a second rising edge while it the same high level of the clock because of the loop is executing faster.

I have developped the same software code but with a 9222 module (AI) which is faster than the 9205 and my actual loop rate varies between 990Hz and 1022Khz and it is due to the clock generation frequency which varies between 990Hz and 1022Khz too.

Reminder : With the 9205, the acual loop rate varies between 860 and 1200Khz.

R. Kaszubiak

09-20-2013 09:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

ah good point. I forgot about that part

- « Previous

-

- 1

- 2

- Next »