- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VeriStand FPGA XML Builder Node Feedback

09-17-2015 09:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

After I had converted an old style Veristand FPGA code to the XML Builder Node I had many problems and unclear error codes, so I found this dscussion. After reading most of the entries and actions (recompilations, XML tweaking etc.etc.) I could think off, I was ready to return to the old style......

As a last resort I created a new Veristand project, everything worked and was ok !!!!

So general tip: make a new project

Regards,

John

09-21-2015 11:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Thierry,

I'm glad that the node eases your development for FPGA with VeriStand. A lot of effort went into creating the node so feedback like that is always great to hear.

As far as moving or changing the inputs/outputs order, that's a surprising involved feature to implement. We'd investigated adding something similar, the ability to add/remove rows throughout the node, but the development effort was very large.

The easiest way we could see to add the functionality would be to allow the importing of XML to configure the node. So if you wanted to move things you could generate the XML, re-order the XML tags either manually or with the tag editor, then re-import the XML to the node. Unfortunately, this feature was never implemented.

Currently, there aren't plans for further development on the node beyond bug fixes and supporting newer versions of LabVIEW and VeriStand. However, please keep the feedback and feature ideas coming and I'll continue to document them.

Thanks!

--Ryan_S

09-21-2015 12:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Wazig,

I'm glad you were able to get everything working! I've converted many "old" style FPGA VIs and projects to use this node and haven't run into issues. However, the node does make certain assumptions about the project and VI so it's possible something had changed that we didn't expect to change and was thereby fixed by generating a new VS FPGA project.

But, when in doubt, starting from a clean project is always a good step! Glad you're up and running!

--Ryan_S

10-08-2015 08:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

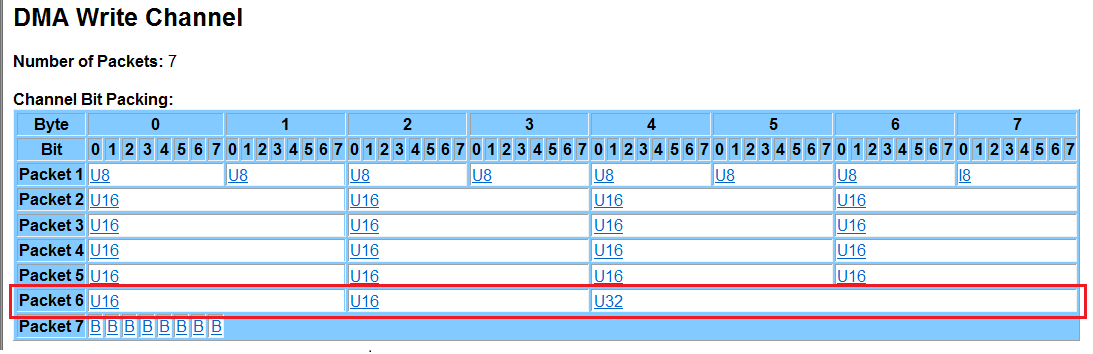

I have found a bug when the node aggregates different data types in the same packet :

For example, the node generates the following packet (from the fpgaconfig file):

The packet 6 first data is named Y5 (U16), the second data is Size_5 (U16) and the third data is Product_ID (U32).

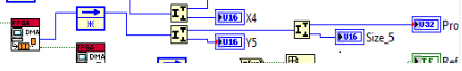

The node generate the following diagram:

We see that the split is wrong (note the coercion).

Regards

Thierry

10-12-2015 12:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Thierry,

Good catch, it does look like we're inverting array elements somewhere. I should be able to take a closer look at this later this week to see if there's a simple fix.

For now, adding another U32 to the end of your node (just a dummy output) should be enough to push those U16's down into their own packet. The other option is to copy the generated code over into your FPGA code and fix the wiring manually.

--Ryan_S

11-20-2015 10:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ryan,

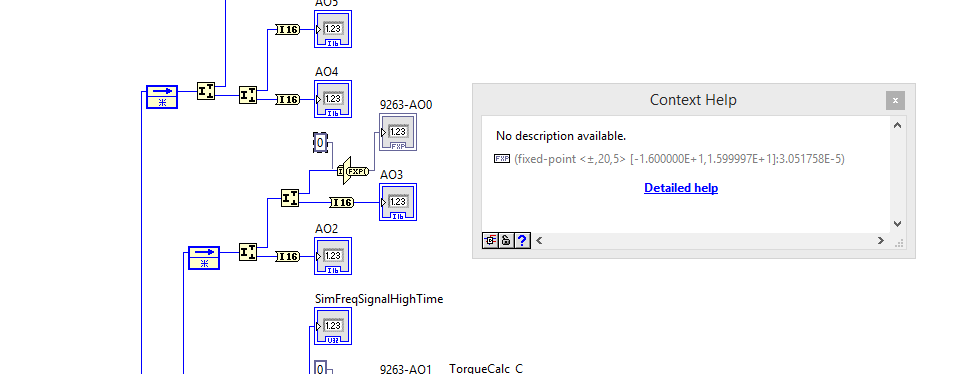

I have a further example where the auto generated code is not quite correct. I am not complaining and I am able to "tweak" the auto generated code, but I wanted to add this "use case" as a test case that you can run the fixes by!! The error is where the FXP I20.5 is trying to be pulled from the a 16bit value, i.e. the "split numbers" is on the wrong branch (AO2 and AO3 should be the output of the split).

The first picture shows the auto generated code, and the second my tweak to correct it. The fpgaconfig xml file is generated correctly and matches my "tweak"ed code, it is just the auto gen code wasn't doing that!!

Auto gen code:

Manual Tweak

By the way, this is an excellent addition to VeriStand FPGA coding - thanks for your time and effort on this.

11-20-2015 06:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey DCatz,

Appreciate the feedback and glad to hear that the node eases your VeriStand FPGA development. I've reproduced the behavior on my end and have added it to the bug list. I likely won't be able to look into the back end code until the new year, but please keep the feedback/bug reports coming.

Thanks! --Ryan_S

11-23-2015 01:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

We stumbled over an issue with U8 variables.

The FPGA code used U8 for some settings, and we discovered that when the value is > 0 in veristand the value in FPGA is always 255. The gain and offset was 1 and 0.

When we changed to U32 no different behaivior, but when we changed to unsigned FXP 8, 8 integer (0-255) everything is working ok !!! ???

Further PWM value's where also not correct (U32 hightime, U32 lowtime ==> U64), we changed this so we transfer Frequency and Dutycycle as FXP value's, and calculate the U32 values in the FPGA.

Do you have an idea what is happening with Unsigned integers?

Veristand 2014, Labview 2014 SP2

11-23-2015 03:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Using a scale of 1 with a U8 doesn't make sense, and is why you're getting odd results. If you just want to pass the value through then you'd use a scale of 255. Please refer to the VeriStand help for scaling values from the FPGA to the host and host to FPGA here. Since FXP is already engineering units, a scale of 1 makes sense and is why that worked in your test.

As for the PWM, I don't quite understand your question, can you ellaborate? With the node, there are two inputs/outputs of the U64, an AI >> U64 and PWM In and AO >> U64 and PWM Out. This defines if the node packs them together (high time & low time) and what it generates for the XML. Please refer to the node getting started guide here for more information on input/output types (there's a note on step 10 that may apply to what you're seeing. Step 16 also discusses scaling and offset and has a link to the same help document I linked above).

Hope that helps! --Ryan_S

03-11-2016 02:30 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I think I may be missing something about how to use this. Trying the attached vi, I get this in my Error log when trying to generate the XML file:

Date: 3/11/2016

Time: 1:11 PM

Error: 1055

Error Source: Property Node in Create and Wire Index for Unpack Booleans.vi->Boolean Outputs for Index Array.vi->XNode_BuildAction.vi->FPGA XML.xnode:GenerateCode.vi->FPGA XML.xnode:GenerateCode.vi.ProxyCaller

No file is generated, but I have to change something in the Node Configuration to re-enable the "Accept Changes & Generate XML" button.