- Document History

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Overview

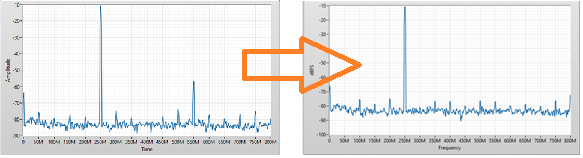

One of the biggest problems with interleaving core ADCs, such as the TI ADC12D800RF used on the NI 5772, is the presence of an interleaving spur at Fs/2-Fin (for dual core ADCs). To effectively squash this spur, we can refine and calibrate the timing between the interleaving ADC cores to give a size-able increase in SFDR:

Attached is an example timing calibration LabVIEW code and documentation that goes over the general operation of the example code and tests done. As a quick overview, the example code looks for an input tone and resulting interleaving spur, then adjusts the core timing to optimize SFDR, and then writes the calibration value to the on-FAM EEPROM. Another VI is provided to be indicative of regular application code that reads the EEPROM value, applies the timing adjustment to the ADC and verifies the SFDR. As well, since the actual sampling timing between the cores is being optimized (as opposed to some spur correction algorithms which apply signal-based DSP), the interleaving spur should be fairly nullified across input frequencies, though it's suggested to run the calibration routine with an input tone indicative of what your application may be for best results.

Description

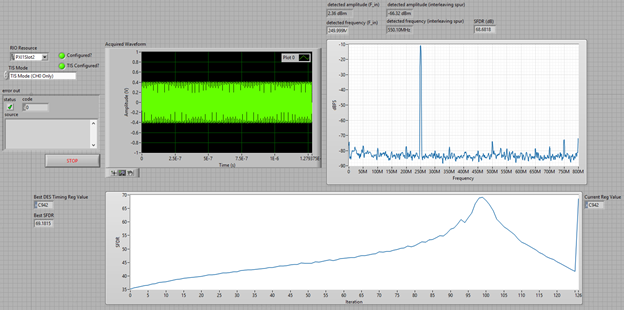

Using the VI NI 5772 (AC) – TIS Mode Setup & Calibrate (Host).vi, the ADC is put through an on-demand calibration cycle and the DES Timing Values (the timing adjustment between rising and falling sample clock edges of the interleaving ADC cores) are iterated through to find the best SFDR.

In this picture, we used an input tone of 1350MHz @ -1dBFS (w/2x 1350MHz LPFs on front-end to remove generator harmonics) to demonstrate the 2nd Nyquist operation in which we saw sub-specification SFDR. Once the best DES Timing Value is found, the value is applied and written to the on-FAM EEPROM (arbitrarily at address 0xF0 in this example).

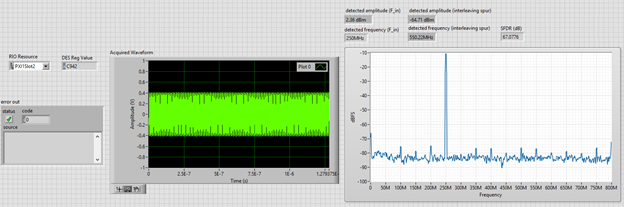

From here, the test VI NI 5772 (AC) – TIS Mode Acquire (Host).vi is used to read from the EEPROM, apply the DES timing values and demonstrate the much better resulting SFDR (here measuring @ 67.1 dBc).

As well, since the routine is finding the best timing values for the interleaving cores, the SFDR is improved across input frequencies.

Hardware and Software Requirements

- LabVIEW 2017

- LabVIEW FPGA Module

- NI 5772 FAM w/FlexRIO Basecard (Bitfile pre-built for NI PXIe-7966R)