From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

03-28-2014 11:31 AM

Yes you could do that. I will require some custom FPGA and XML code made by you.

You basically want to add an IO property node to the diagram where you set the IO mode programmatically. You can then add a parameter to each of your analog IO channels so you can tune this from system explorer as a parameter.

If you go to the RIO library and see one of the specialty analog modules like the 9234, this technique is used to set the rate of the module. You will want to do something similar

03-31-2014 06:44 AM

Yes, I would like to add an IO property node to the diagram and set the value programmatically from a Veristand channel parameter. I understood how to add a parameter to a channel thanks to your answer and the Veristand help.

It remains one problem, none property or method is available in my LabVIEW FPGA diagram for the analog inputs of the PXI-7841R board.

Is it possible to modify the configuration mode programmatically for the PXI-7841R device? Have you got an exemple?

Best regards

03-31-2014 09:02 AM

Hey DMous,

This is more of a LV FPGA question. I would search the help. Its there somewhere. Alternatively you can contact support at ni.com/support

11-09-2015 04:02 AM

Hi,

I have a question about .fpgaconfig file.

Are there manual for how to write .fpgaconfig file?

Or, are there any tools that automatically creates .fpgaconfig file?

The reason why I am asking is when the customer want to create more packets (about 60 packets), he needs manually edited .fpgaconfig file by himself.

It did not work properly at first, but when he upside-down the order of packets, it began working.

They are wondering what was wrong with .fpgaconfig file.

Please let me know if you have any information for this behavior.

Regards,

Haruka

02-22-2016 10:19 AM

Hi Stephen,

I have some doubts regarding how develop CAN communication using the tool.

Based on to the CAN communication be used in Veristand to send and receive frames and perform actions according to the frames received.

To create FPGA-Based I/O personalities I am using FPGA XML Builder Node Add-on. Using this add-on or the other way using DMA´s the input and output that I can connect are AI (analog input), AO, DI and DO (Digital output). But I will like to work with the CAN module N-9853 that give me and output in cluster mode or U6 32 array.

My firs doubt:

I don´t see how I can implement that customizing FPGA interface

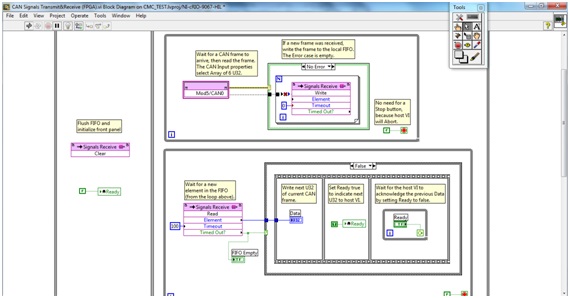

This is the code that I have developed for the FPGA for read/write using the module N-9853.

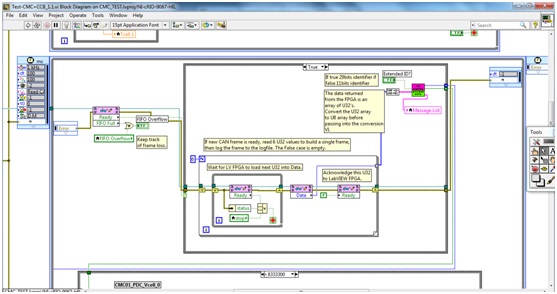

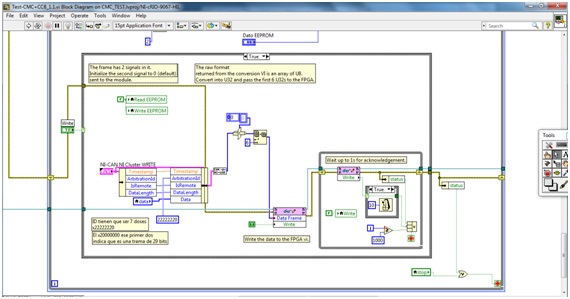

And this is how I develop the read/write in Real Time in labview

Finally some other doubts:

Is it possible to do this using Veristand? Is it possible to link programs from labview with veristand? If yes, How would be they communicated for data transfer?

Thank you in advance!!

03-02-2016 03:51 PM

Hi, I am using cRIO 9038 (RT Linux64) with NI 9381 (AIO/DIO) in slot 1. I created a fpga personality and added to a VeriStand project. Everything went smoothly until I tried to deploy it. I am getting the following error.

Details:

Error 61060 occurred at Project Window.lvlib:Project Window.vi >> Project Window.lvlib:Command Loop.vi >> NI_VS Workspace ExecutionAPI.lvlib:NI VeriStand - Connect to System.vi

Possible reason(s):

LabVIEW FPGA: The Wait on IRQ method timed out before the specified interrupt was received.

=========================

NI VeriStand: FPGA DMA.lvlib:Wait on IRQ from FPGA.vi:3760001<APPEND>

Complete call chain:

FPGA DMA.lvlib:Wait on IRQ from FPGA.vi:3760001

HP Loop.lvlib:HP Loop Main.vi

NI VeriStand Engine.lvlib:VeriStand Engine State Machine.vi

NI VeriStand Engine.lvlib:VeriStand Engine.vi

NI VeriStand Engine.lvlib:VeriStand Engine Wrapper (RT).vi

I only modified the input and output section of the template. Any suggestion is appriciated.

Thanks.

03-20-2016 08:20 AM

Hi mtitoo, I got excatly the same issue as yours, VeriStand keeps telling me about this time out error. Did you solve this problem in the end?

Thanks.

03-25-2016 03:16 PM

Hi Ethanlu2, I have not got a chance to play with this tool. However, I was talking to one of our fellow LabVIEW experts on that issue yesterday and he pinpointed one probable cause for this. When template generates the FPGA project, the incoming packet number is 11, however I had only 4 packets but forgot to change the for loop iteration from 11 to 4. Did you have something like that? If you had, make sure FIFO read iteration matches your number of packets in XML file and give it a try.

03-25-2016 08:58 PM

That's exactly the mistake I have made. Thank u so much. ![]()

05-23-2016 02:03 AM

Hello,

My customer is trying to understand how Custom Personality FPGA.vi in the template works. Specifically, he is looking at Packet 1 free label section of the diagram where the output "Is Late?" from "NI VeriStand - Synchronize to Host.vi" is written to "NI VeriStand - Send Packet to Host.vi" as Packet 1. In Custom Personality.fpgaconfig file, Packet 1 is not included in the channel of system definition file. In order to look at Packet 1 information, does he need to modify fpgaconfig file manually, or is there any way to look at it since it is written to DMA FIFO?

Also, "8 PulseMeasurements.vi" has Timeout as input parameter. What happens to the output values when timeout occurs? We were looking at the following help document but PWM in the table doesn't indicate default value.

By the way, above help says that default value for offset is 1. Is this supposed to be 0 instead of 1?

Regards,

Michi