- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このスレッドを最上位に表示

- {0}にこのスレッドを追加する

- 購読

- ミュート

- 印刷用ページに変更

LabVIEW FPGA Xilinx IP "DFT" の使用リソース量について

12-15-2016 03:53 AM

- 新着としてマーク

- {0}にこのメッセージを追加する。

- 購読

- ミュート

- RSS フィードを購読する

- このメッセージをハイライトする

- このメッセージを印刷する

- 管理者に不正使用を報告する

いつもお世話になっております。表題にありますようにLabVIEW FPGA Xilinx IP "DFT" の使用リソース量について質問です。

LabVIEW 2016 を使用しており、ターゲットデバイスは、 FlexRIO PXIe-7976R (Kintex7 410T) になります。

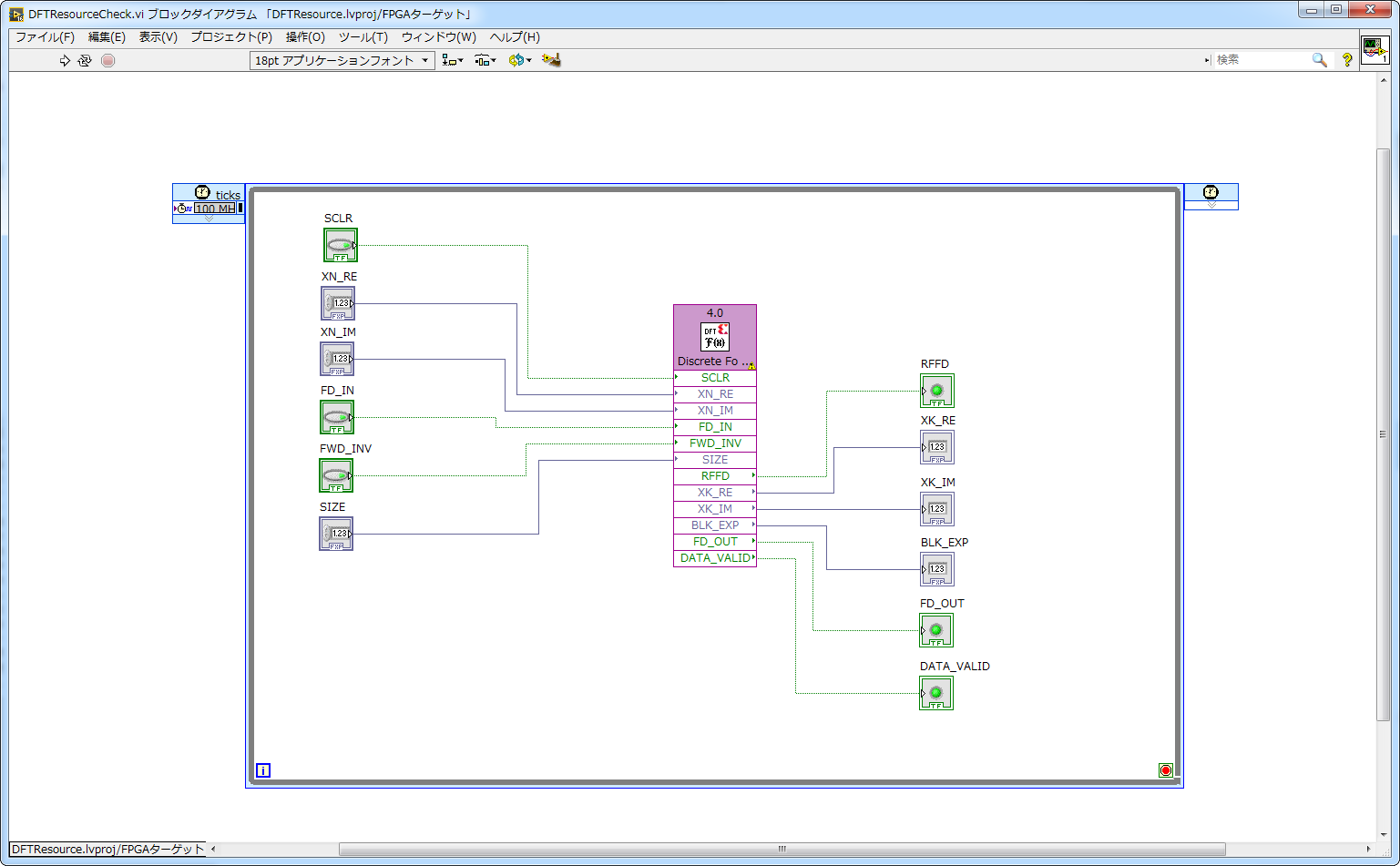

Xilinx IP コアである "DFT" の単体でのリソース消費量はどの程度か確認しようと思い、以下のような単純な VI を作成しました。

DFT コアの入出力を制御器、表示器に接続し、SCTL で囲っただけのシンプルな VI です。

Xilinx のサイトに DFT コアの使用リソースが掲載されていたのですが、実際にコンパイルしてみると大幅に スライス LUT やレジスタ、メモリの消費量が異なります。

https://japan.xilinx.com/support/documentation/ip_documentation/ru/dft.html

Xilinx サイトでは、抜粋いたしますと、デバイスは Kintex7 480T と異なるものの同じパラメータで以下のようになっていました。

----

LUTs 3973

FFs 4568

LUT-FF Pairs 2730

DSP48s 16

36k BRAMs 3

18k BRAMs 4

----

しかし、上記の VI を LabVIEW FPGA でコンパイルすると、

---

スライス LUT 57857

スライスレジスタ 55334

合計スライス 21301

DSP48s 16

ブロックRAM 121

----

のように、DSP48s 以外は大幅に異なります。

複数 DFT コア (20個以上) を実装して使用したいと思っていたのですが、このリソース消費量ですとせいぜい 3個が限界のように思えます。

Xilinx サイトのリソース消費量ならかなりの数を実装できるように思えたのですが。

こうなってしまう原因はどこにありますでしょうか。

そもそも Xilinx サイトのリソース表示が間違っているのでしょうか。

それとも、LabVIEW FPGA では、DFT コア以外に見えないところ(ホストとのやり取りなど)で初めからかなりのリソースが消費されているのでしょうか。

ご回答いただけると大変助かります。よろしくお願い致します。

12-16-2016 12:21 AM

- 新着としてマーク

- {0}にこのメッセージを追加する。

- 購読

- ミュート

- RSS フィードを購読する

- このメッセージをハイライトする

- このメッセージを印刷する

- 管理者に不正使用を報告する

昨日質問したものです。

その後、さらに単純な SCTL だけの VI を作成してコンパイルしたところ、以下のようなリソース使用量になりました。

これをコンパイルしたところ、以下の結果となりました。

なにも VI になくてもこれだけのリソースは消費されていることがわかりました。

先日の DFT でのリソース使用量から差し引くと、概ね Xilinx サイトでの DFT リソース使用量であることが分かりました。

お騒がせいたしました。

この最初から消費されているリソース量はいったい何に消費されているのかは分からないままですが。。。

(ホストとのインターフェースなどで使われていると勝手に想像しております)