- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI-FPGA 1473R and Hamamatsu Flash4.0 V2 data transfer problem

11-12-2014 09:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, Sir:

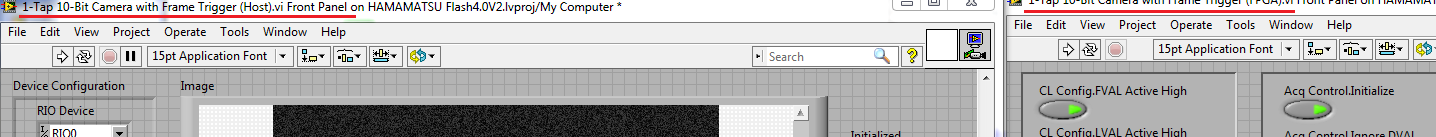

I use NI FPGA 1473R-LX110 board to connect with Hamamatsu Flash 4.0 V2 camera.

The camera is 10 tap 8bit with two MDR cameralink interface.

But the return image is like attachment.

The image is not right.

Do you know where is the problem?

The example is from the NI FPGA example.

11-13-2014 12:43 AM - edited 11-13-2014 12:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Your snapshot indicates that the example you are using is for one One-Tap 10-bits camera.

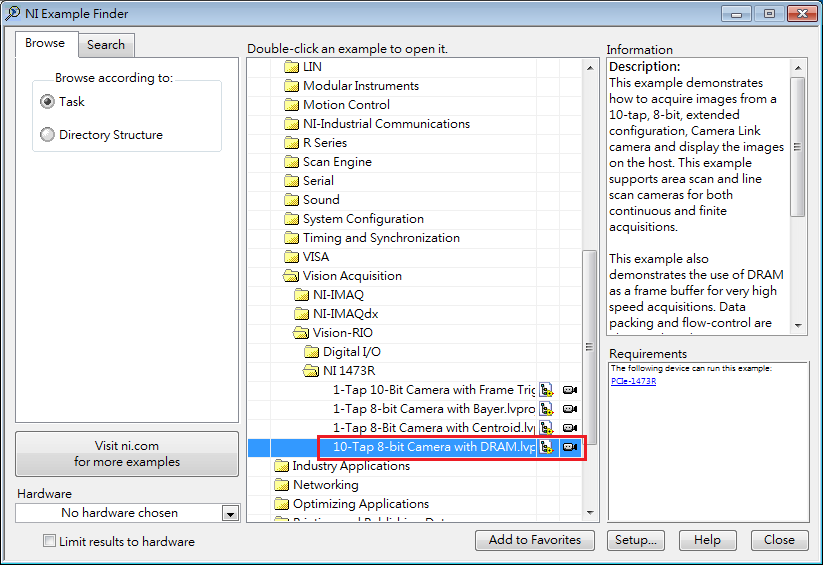

I suggest you to select a correspond example that fit for 10 tap 8bit camera.

11-14-2014 05:39 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, Ting:

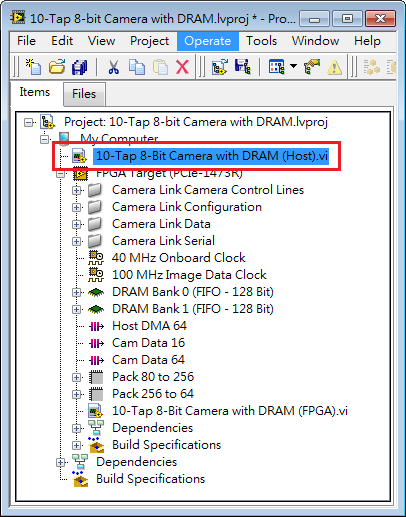

I tried to use this example.

But the image is still incorrect.

I also asked Hamamatsu engineer.

Below is their response.

Flash 4.0 has very specific data read out.

Top half of image, line data output order is from center to top, and bottom half of the image, line date order is center to bottom.

Do you have any ideal for this problem?

11-16-2014 10:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Do you have NI PCIe-1433 or PCIe-1435?

It would be much easier to use these ready-to-use CameraLink cards.

It seems there are some built-in cam files let you to config the camera.

If you can only use 1473R, and you don't have any other option, then you might have to modify the FPGA part by yourself.

It would be very difficult to do this. You camera FAE has to cowork with you to make this work.

11-18-2014 06:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Those Orca .icd files appear to be for a much older camera, and I'm pretty sure would not work for the Orca Flash 4.0 V2. However if the issue is simply the line ordering, then I presume that you could acquire the out-of-order image, and then reorder the lines downstream.

However it does appear that any of these cards, or the 1483R FlexRIO, all support 10-tap 80-bit acquisition at 85MHz which appears to be enough to acquire at the full frame rate, though I have not seen any official confirmation that the Orca Flash 4.0 V2 is supported - can anyone confirm? Our local Hamamatsu rep thought not, but he was not familiar with the NI products.