- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

myRIO FPGA VI and RT VI problem

10-29-2016 05:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

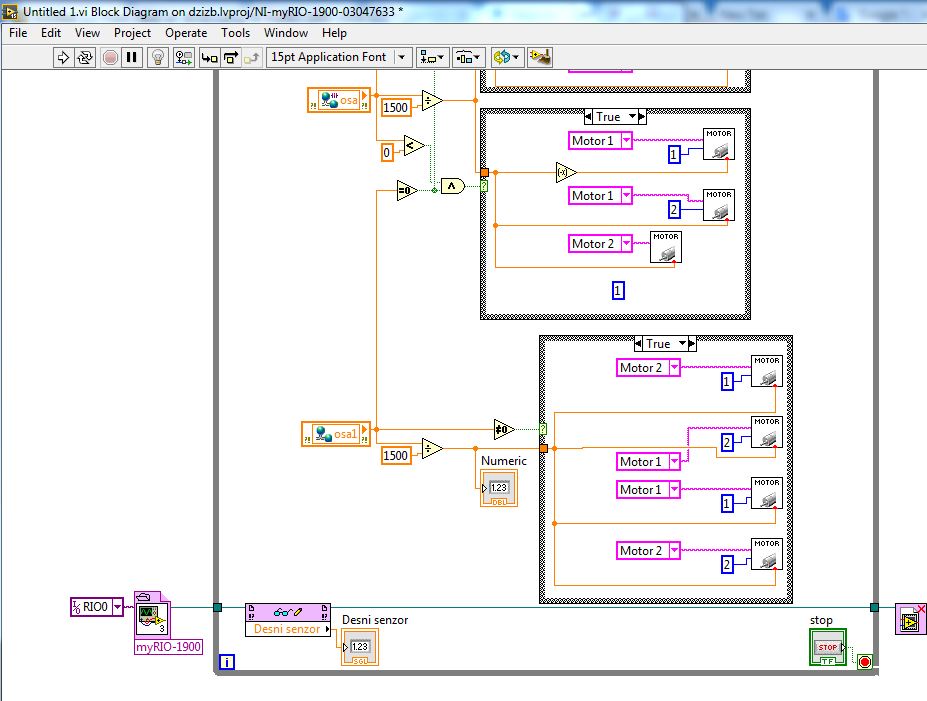

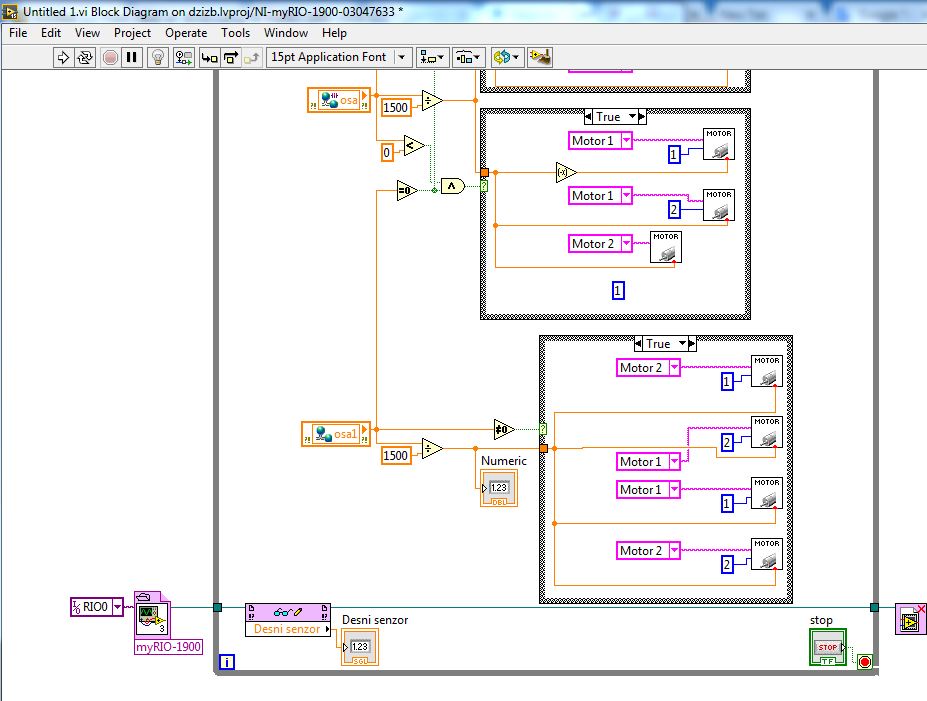

I tried it too, and I get reading from the sensor in my RT VI using open fpga reference, but other parts of that RT VI does not work. Part of the code which relates to motor does not work, I tried and inserting only a simple code that blinks the LED on myRIO but that dont work too. I have no idea what to do. Have you any idea ?

Regards

10-29-2016 05:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I tried it too, and I get reading from the sensor in my RT VI using open fpga reference, but other parts of that RT VI does not work. Part of the code which relates to motor does not work, I tried and inserting only a simple code that blinks the LED on myRIO but that dont work too. I have no idea what to do.

Regards

10-29-2016 05:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Did you do everything I suggested in that thread, such as putting ALL IOs in the FPGA VI? That will work for sure.

10-29-2016 06:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

How can I do that ? Why this is not working like I do before ? It is more complicated to do it like you tell ? Can you sent any example ?

Regards

10-29-2016 07:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

1. FPGA VIs don't have a UI, unless for when you run it in interactive mode.

2. The reason it won't work is that you cannot run two VIs at once, that's why you have to get everything in one.

3. If you still don't understand, I can send an example.

10-29-2016 07:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Problem is in that I dont have some function in FPGA VI so I cant have only one VI. Is there any way to use two or more VI and FPGA VI ? If you have any examples sent it to me please.

Regards, and thanks you very much for help.

10-29-2016 11:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Let's take a high level look at the RIO architecture.

You have three general components: FPGA, RT, Host PC

The FPGA is responsible for handling all of the IO. Even if you skip the FPGA, LV will create a bitfile for you to handle the IO only portion. But, at the base, you're going to have all of your IO come directly from the FPGA simply because that's what it's hooked up to.

As the FPGA is a hardware implementation, it doesn't always make sense to handle all of your IO processing here. But, it's still nice to have the strength of a RT OS. This is where your RT comes in. You can process the IO without actually modifying it directly. You do this by passing things back and forth from the FPGA to the RT through means like User Defined Variables or more commonly FIFO buffers (please make it a habit to use the latter when possible) You can leverage this functionality to get the data from the FPGA and then do all of the analysis you'd like on the RT.

When you want to see things on your PC, you need to send data back and forth from the RT (or the FPGA) to the Host PC. You'd use things like Network Published Shared Variables or Network Streams to accomplish this task.

When he's saying put all of the IO on the FPGA, it's because if you try to split the IO between the RT VI and the FPGA VI, you're telling the RIO that you need to have two separate hardware implementations running on the FPGA at once. That simply can't happen. You just need to take some time to understand how to pass data from the FPGA to the RT so that you can use that to make changes to your values. Once you have that in place, you can put all of the IO on the FPGA and still gain the value from the RT.

11-03-2016 02:43 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I try a few days to do my work, but I dont have any sucess, can you tsend me an example of how it would look in FPGA mode for ultrasonic sensor HC-SR04, which I use in the project, but it I also can be used RT VI, or sent me a similar example. Because we were just paralyzed with the project and we have still a lot of work

11-25-2016 05:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It is the same problem I was having. if you have a sample sent it to me please.

05-03-2020 05:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, I'm having a similar problem. Can you send me a sample of how it runs in FPGA and RT both