- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Using Sub-VI in FPGA possible?

09-05-2008 07:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I have a few FPGA VI's that contains AI, AO, or DO (the way I wanted to group them). Now, I have put these FPGA VI's as sub VI's in a top-level FPGA VI, and have linked them up like you normally would in other non FPGA Labview programs. Then, I would compile it, and put a Open Reference, Read/Write, Close Reference, in the RT VI. And.... it doesn't work.

Is there a way to use sub-FPGA VI's? It would be rather crazy to try to fit all 96 DIO controls into one top-level FPGA VI. Thank you.

09-06-2008 03:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello ExpoEra,

of cause you can use Sub-VIs in FPGA. There is no diffrence to non-FPGA code.

Can you explain more in detail what does not work? Is there an error message or error code?

What hardware do you use? Can you upload a picture of your code or the VI?

Uli

09-08-2008 11:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I simply took the example Analog Input VI, used it as a sub-VI in another FPGA VI, and ran it in the host RT VI using Open Reference. Maybe, it'd be more clear if I post a screen shot.

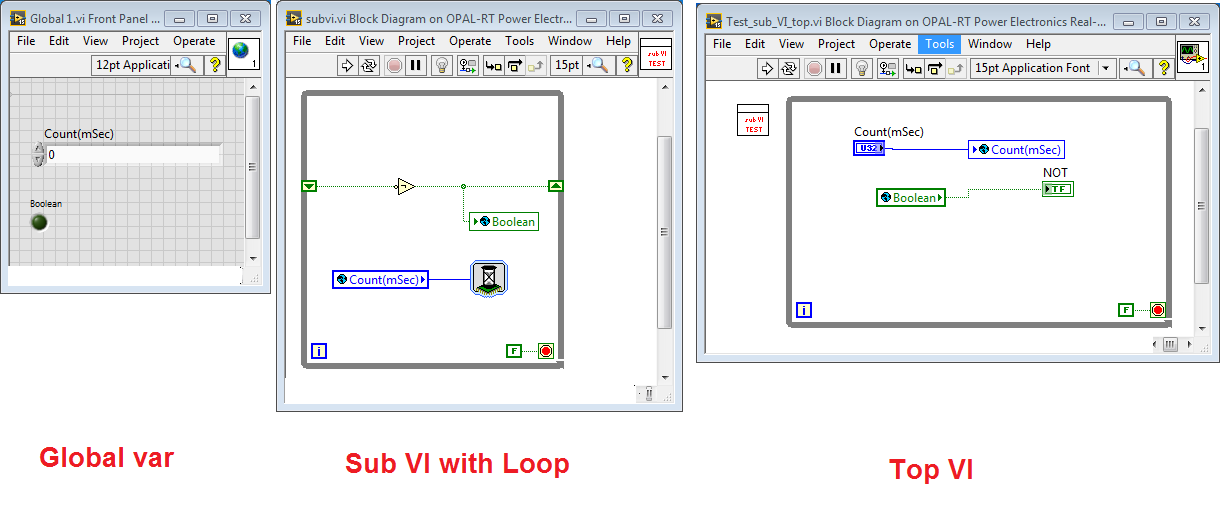

The first one is the sub FPGA VI, the middle one is the top level FPGA VI which contains the sub VI, and the last one is the RT VI.

I hope I haven't confused anyone.

09-08-2008 11:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ExpoEra,

You can definitely use another FPGA VI as a sub-VI--however, always remember that as the FPGA is meant for combinatorial operations, your sequential operations in the sub-VI can be somewhat computationally expensive. Also, I noticed that the master level VI looks like you want to do a one-time operation. Is that how your VI is designed?

Ipshita C.

Applications Engineer

09-09-2008 01:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi there,

What exactly is not working? Is it the compiler that gives you an error, or is it the program that does not answer to the host PC?

One thing that you could do is to verify that your interupt code is working properly (that you aknowledge it and so on).

Also, in your while loop on the FPGA, you could wire up a constant instead of a boolean control, this is probably consuming less ressources on the FPGA.

The use of the sequence on the FPGA should not be an issue. (it is on non FPGA system)

09-09-2008 08:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If the top screen shot is really what is contained in your sub VI, then your problem is that the subVI will never return. When a subVI executes it only reads it's inputs at the start of the subVI, and only updates it's outputs after the subVI completes. In this case the stop control will be FALSE when the subVI is called, so the subVI will continue to execute forever without stopping because Stop is always FALSE. The outputs will therefore never get updated and your host will always read whatever you have the default value set to (presumably 0s).

What your really want to do is make the sequence structure the subVI, and move the while loop to the top level VI. That way the subVI will execute over and over again and update it's input (Loop Rate) and outputs (FPGA Error Out and AI Data) each iteration. I would also strongly advise moving the IRQ to the top level since it is controlling communications to your host, which is done by the top level VI.

Hope this helps-

Dustin

09-09-2008 12:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If the top screen shot is really what is contained in your sub VI, then your problem is that the subVI will never return. When a subVI executes it only reads it's inputs at the start of the subVI, and only updates it's outputs after the subVI completes. In this case the stop control will be FALSE when the subVI is called, so the subVI will continue to execute forever without stopping because Stop is always FALSE. The outputs will therefore never get updated and your host will always read whatever you have the default value set to (presumably 0s).

What your really want to do is make the sequence structure the subVI, and move the while loop to the top level VI. That way the subVI will execute over and over again and update it's input (Loop Rate) and outputs (FPGA Error Out and AI Data) each iteration. I would also strongly advise moving the IRQ to the top level since it is controlling communications to your host, which is done by the top level VI.

Hope this helps-

Dustin

Ok. I have changed it as you have suggested, and it works now. Thank you.

12-08-2015 02:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

One can use global variable to pass data into and out of a loop inside subVI during execution from top VI.

The following examples shows how to do this:

https://decibel.ni.com/content/docs/DOC-19962

12-08-2015 04:46 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

See the attached codes.