- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Slow timed controlled loop for DMA transfert

06-26-2014 03:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hello,

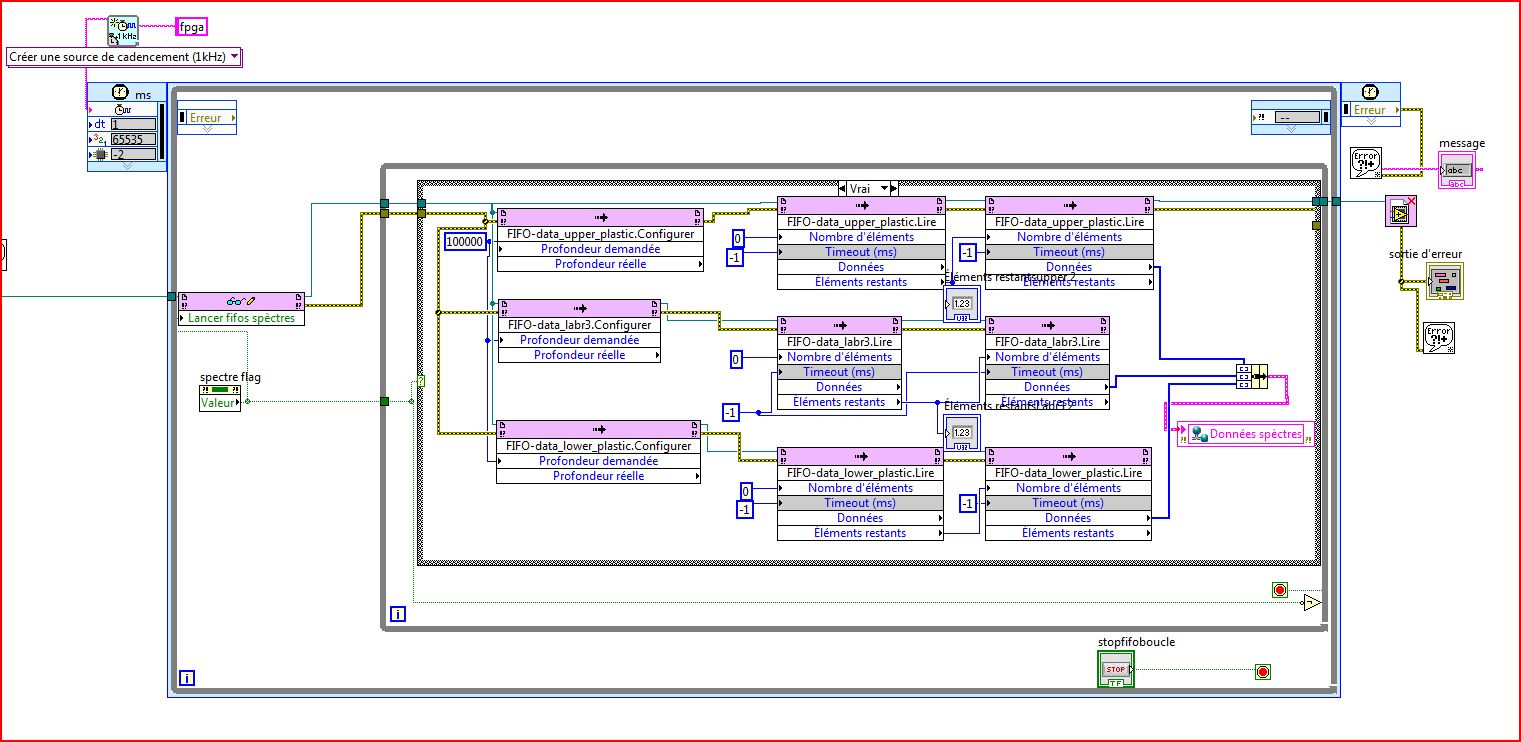

I am using a timed controlled while loop to empty my DMA FIFO in order to get the data from my FPGA.

Problem:9 times out of 10 my timed controlled while loop (set to 1kHz) runs very slow (approx.1Hz) and the data I get from my FIFO is uncorrect (very few data points, and values messing)

Is it a computer ressource problem?

Why is my time controlled while loop so slow?

06-26-2014 03:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Did you check the error clusters?

The best solution is the one you find it by yourself

06-26-2014 04:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

Yes I did, and there is nothing

06-26-2014 08:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You shouldn't be constantly recofiguring your FIFO. Those Configures should be done before your loop.

And why do you have a While loop inside of your timed loop? Even worse, if your flag is set to TRUE, that While loop will never complete.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

06-26-2014 09:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Some thoughts:

First, a timed loop will attempt to hit exactly the rate you specify. That is, it isnt a problem that you hit 1 ms 9 times out of 10, its a problem that you *only* hit it 9 times out of 10.

Generally speaking I don't use timed loops with fifos. There is no need. FIFOs are not used for deterministic control (usually, I suppose).

Timed loops are put at the highest priority in the system, it is generally not a good plan to put a UI-related node inside (your property node). In general, UI-related nodes should not be used on RT at all. If this system isn't RT, you shouldn't be using a timed loop, as the determinism you are capable of getting is horrible.

Read through some of http://www.ni.com/compactriodevguide, esp section 3 which talks about the FPGA interface, including FIFOs. (NOTE: Even if you are not using cRIO this section has valid parts to it, just skim past the hardware specifics).

You are getting very odd datasets because you are not specifying a number of data elements to read. It looks like you have three data channels you want to be synchronized. They won't be synchronized unless you request the same amount of data from each (or some multiple, if the rates are a multiple of each other).

Configuring the fifo on every iteration is potentially clearing the buffer, and definitely causing a slowdown, and probably causing data loss from backing up the fifo.

Putting a case structure around your fifo is not a great plan, from what I can tell. Data will still be streaming in from the FPGA unless you stop it, so all you've done here is decided not to read it. One option is to just put the case structure around your variable, so you always read the data but only sometimes send it across the network.

Sending data across the network in a timed loop is not a good idea. Again, see the cRIO developer guide linked above for a discussion of networking in section 2.

Shared variables are current value only, and fifos are streaming data. If you are OK with this, thats fine. If that sounds like a bad idea to you and you have different goals, check out pg 52 of section 2 of the crio developer guide.