- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RT FIFOs and data logging

07-15-2013 08:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

I am trying to use my RIO FPGAs and DMAS, FIFOs etc to read some analog inputs and log the data in a tdms file. I have followed a basic labview example yet my code is not working as it should; on clicking 'run' an error (61003) is obtained from the fifo read and the program stops. Can anyone see an obvious reason why?

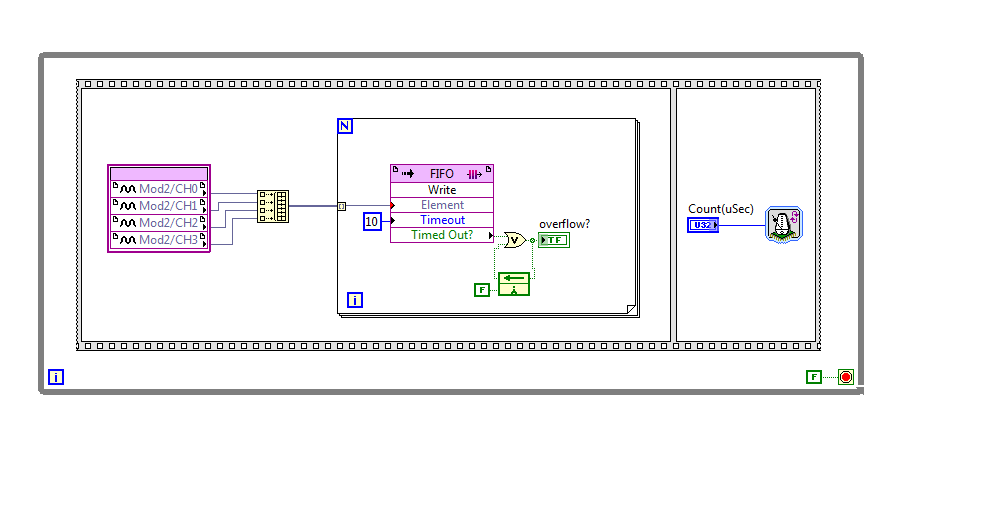

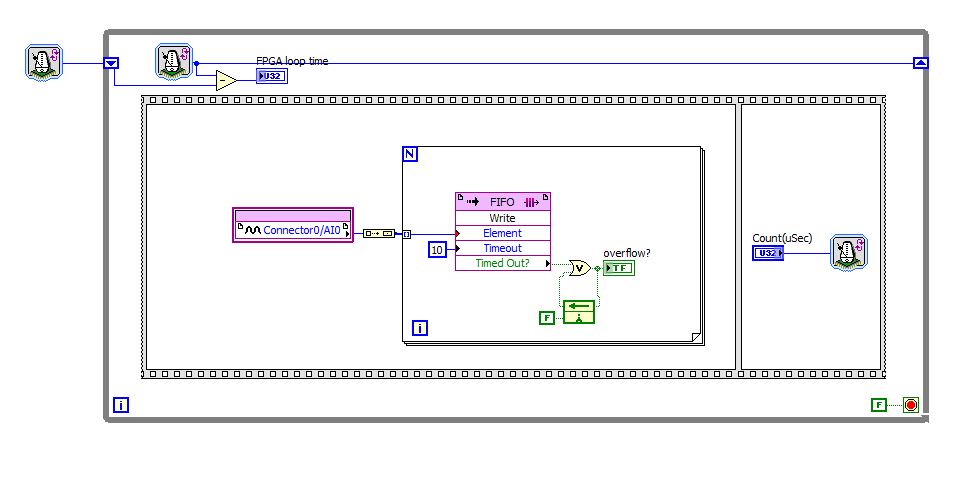

The FPGA Code:

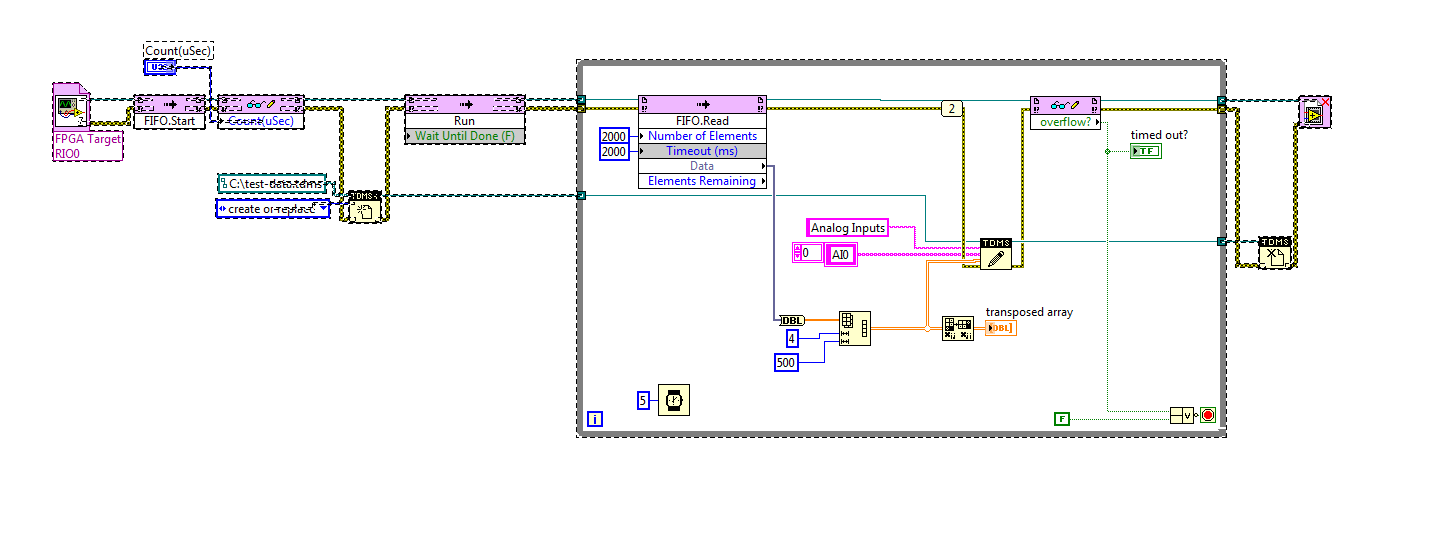

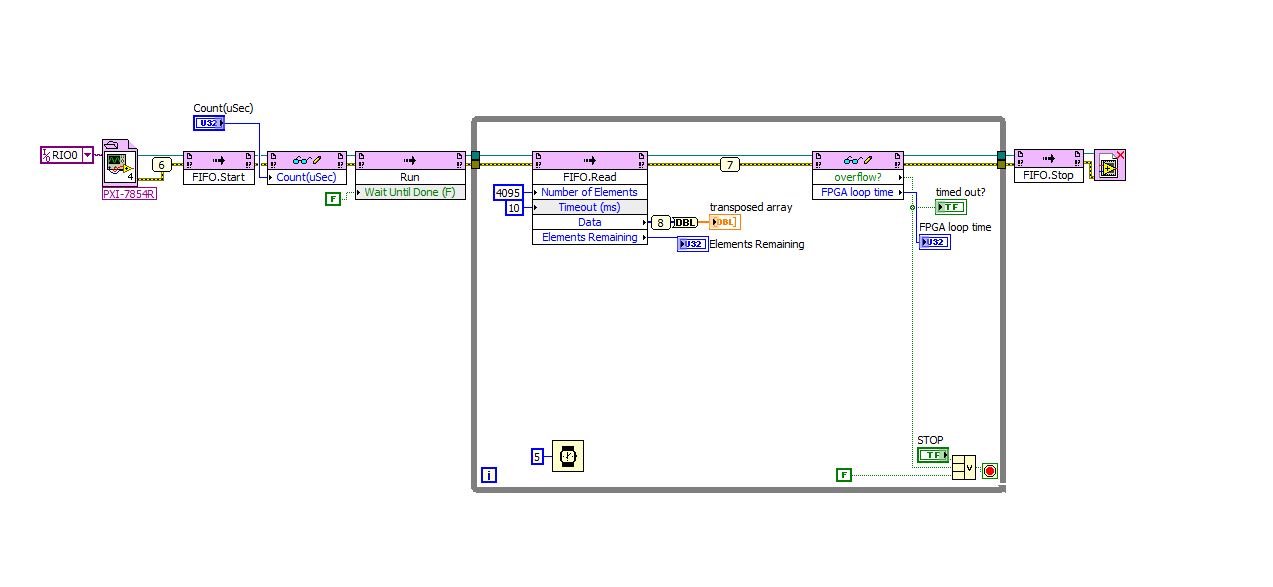

and the RT code

07-15-2013 08:58 AM - edited 07-15-2013 09:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Boileroo

It's worth checking that your FPGA reference isn't set to 'Open and Run' instead of just 'Open, since when you reach the 'Run' node in your code it would return error 61003 as your have described.

It's also worth recompiling your FPGA VI just to make sure nothing is corrupted there.

Kind Regards

07-15-2013 09:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

alas no unfortunately not, that was my thought too!

07-15-2013 09:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Could you attach your actual VI/project so I can try to run it here?

Kind regards

07-15-2013 09:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm afraid I cant! My place of work has very strict rules governing the upload/download of files. Sorry!

07-15-2013 09:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

No worries.

The error code relates to already having the FPGA reference open, so somewhere along the lines it's getting opened twice (attempted).

To be certain:

1) 'Run the FPGA VI' is unticked on 'Configure FPGA VI reference'

2) 'Run when opened' is unticked on the FPGA VI properties, under the category execution.

3) Have you tried enabling 'Wait until done' (T) on the Run node?

4) Alternatively try removing the Run node, since the error implies that it's already running.

As an aside I notice you're also missing FIFO.Stop from the DMA FIFO example.

Kind Regards

07-17-2013 09:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

thanks a lot. with the above things I finaly was able to get it all to work as it should!

I have a couple of quick questions regarding the use of DMA FIFOs. It seems to me that the variables we have control over in this sort of instance are:

-The speed of the FPGA Loop. In this case wish to sample at 500 kHz so this is 2 usec

-The size of the FIFO buffer, both on the RT system and the FPGA

-The number of elements read from the FIFO with each RT iteration

Is anyone able to explain to me how to go about sizng these things? I have managed to get it working through arbitrary tweaking of the above parameters but am not happy that I understand how it all works!

Many thanks