- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Question Regarding DSTARA from 6674T to FlexRIO 7966R and FAM AT-1120 Module

Solved!02-12-2015 12:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I have a PXIe-1085 Chassis and the following boards installed:

Slot 10: PXIe-6674T Timing Module

Slot 02: PXIe-7966R FPGA

Attached to the PXIe-7966R FPGA Is an AT1120 adapter module.

I'm trying to supply a 125 MHz clock from the DDS output of the 6674T to the backplane in order to the feed the DSTARA clock to the PXIe-7966R and subsequently to the AT1120 adapter module as the DAC clock.

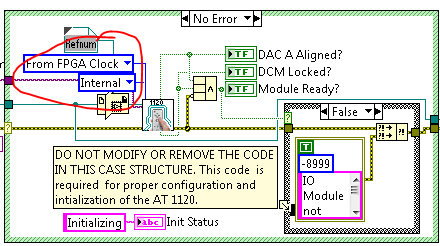

I'm currently using a modified version of the AT-1120 Getting Started project (https://decibel.ni.com/content/docs/DOC-26331) and have the Adapter Module set to take an internal clock and from FPGA clock as specified in the AT-1120 user manual:

For my adapter module CLIP on the FPGA VI I have the clockin set to the DStarA Clock as shown below:

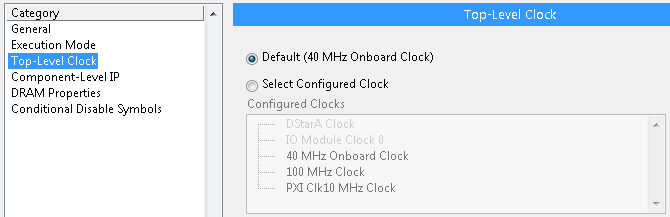

For my adapter module CLIP on the FPGA VI I have the clockin set to the DStarA Clock as shown below: For my FlexRIO 7966R I have the toplevel clock set to the defautl 40 MHz onboard clock. I cannot use an external clock for this:

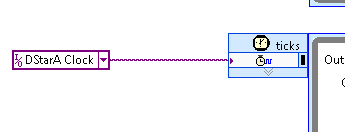

For my FlexRIO 7966R I have the toplevel clock set to the defautl 40 MHz onboard clock. I cannot use an external clock for this: Then I have my SCTL clock set to the DStarA Clock:

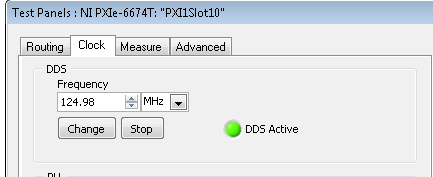

Then I have my SCTL clock set to the DStarA Clock: For simplicty sake, I am trying to feed the DSTARA clock using the test panel in NI Max with 6674T as follows. Becuase my FPGA is in slot 2 on the 1085 Chassis, I am feeding the 125 MHz DDS frequency to PXIe_DStarA6 based on the PXIe-1085 user manuel (http://www.ni.com/pdf/manuals/373712e.pdf) specified timing DStar lines:

For simplicty sake, I am trying to feed the DSTARA clock using the test panel in NI Max with 6674T as follows. Becuase my FPGA is in slot 2 on the 1085 Chassis, I am feeding the 125 MHz DDS frequency to PXIe_DStarA6 based on the PXIe-1085 user manuel (http://www.ni.com/pdf/manuals/373712e.pdf) specified timing DStar lines:

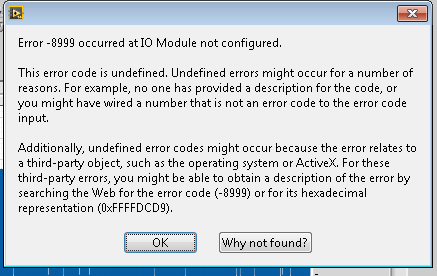

However, when I try and run my VI with all of these settings I get the following error:

However, when I try and run my VI with all of these settings I get the following error: Has anyone seen this, or can anyone advise regarding this? Maybe I'm using the DStarA lines wrong or something, but I'm not sure. Any help or suggestions from the community would be great! Thanks for all your help! -GMac

Has anyone seen this, or can anyone advise regarding this? Maybe I'm using the DStarA lines wrong or something, but I'm not sure. Any help or suggestions from the community would be great! Thanks for all your help! -GMac

Solved! Go to Solution.

02-12-2015 03:35 PM - edited 02-12-2015 03:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

GMac,

Hello!

There are three things that I think in combination will resolve this issue.

1. ) You may not have included it in your screenshots, but there is an additional step that you must do to use DSTAR A. The bitfile you are using must be complied with a setting that tells the FlexRIO to use the DSTARA signal.

- Right Click on the Adapter Module in your project and go to properties

- Go to the details category

- Make sure, "PXIe_DStarA" is selected in the "IoModSyncClock" section.

- If it is selected, then you have probably already selected this and compiled your bitfile. If it is not selected, or you are not sure if you compiled the setting, Re-compile your Bitfile.

2.) Also, The issue you are seeing was a known issue that was fixed in Active Techonologies (AT) latest software update (version 1.8). While I am not 100% certain, I do not think the Getting Started Example has been updated to contain all the VIs from ATs software update. Likewise, the bitfiles provided with that example would not have been generated with the CLIP included in the latest software version.

I would suggest the following:

- Download the latest version of the AT software (version 1.8) from their website

- Use the example that comes with their software to confirm that you can clock to DSTARA

- Update our Getting Started Example to use the latest software. (generate new bitfies, replace old AT VIs in project directory with new VIs)

- Confirm your new example works.

3.) Generate a 125MHz signal from the 6674T, not 124.98MHz. The hardware is expecting a 125MHz signal. The dialog window says 124.98MHz due to a workaround for an odd sitiuation that was causing compilation failures. If you'd like more info on this, let me know and I'll fill you in. read this forum post: http://forums.ni.com/t5/LabVIEW/7966R-DSTARA-Clock-and-AT-1120/m-p/2932916#M847692

I hope this helps!

Ben Sisney

FlexRIO V&V Engineer

National Instruments

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

02-12-2015 05:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Ben,

You are correct, it was a two-fold issue, I needed to set the io mod sync clock on my adapter module clip properties, and I also needed the updated VI's from version 1_8 from Active Technologies. After that it worked great!

Thanks for your help!

Best,

-GMac

02-13-2015 08:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

GMac,

Glad to be able to help!

Ben Sisney

FlexRIO V&V Engineer

National Instruments

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

03-29-2015 05:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Ben,

I have another question regarding the updated software/code for the AT-1120.

It seems now that when I stop the VI, and try to re-run it (a modified version of the getting started again), it throws an errror (DCM doesn't lock and DAC is not aligned). However on another re-run of the VI it works fine again. That is every other re-start works fine, the alternating re-starts of the VI fail. Any idea why this may be? do you think it's another software change from Actiive Technologies? I didn't see this issue with the previous VIs/code.

Any advisement woud be great.

Best Regards,

-Gmac

04-01-2015 11:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Gmac,

That is odd! I haven't seen that behavior before and wouldn't expect that to be the correct behavior either.

Do you see the same behavior if you use the examples that ship with the AT software rather than the updated/modified getting started example?

Ben Sisney

FlexRIO V&V Engineer

National Instruments

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

05-05-2015 07:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ben,

I was able to solve this issue a while back, my apologies for not responding sooner!. If I did not reset the 6674T and/or set it up before running the FAM and FPGA, then that is when the issue occured.

Best,

-Gmac

05-06-2015 09:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Gmac,

Glad you were able to figure it out! Thanks for posting back to let everybody know what the root cause was.

Have a great day!

Ben Sisney

FlexRIO V&V Engineer

National Instruments

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -