- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Processing acquired data (8 simultaneous channels) in RT host (producer,consumer problem)

07-08-2014 01:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Gents,

I have a Crio 9024 and two delta sigma modules NI 9234, I have to acquire 8 cahnnels simultaneously at 51,2 kHz from FPGA and transfert this data via DMA fifo to the RT host for proceesing (FFT for all channels and send data to a host computer via a stream network). I succeed to do this with 25,6KHz as sampling frequency but when I tried with 51,2KHz (my goal) I had problem because in RT code I have a producer loop receiveing data from fpga (DMA fifo) and sending this data to a consumer (Queue) loop in RT also for processing this data but the producer is to fast so the consumer loop can't proccess data in time and the queue is overflow. I have replaced queues with RT fifo,single process variable,... but no luck !!!

Any way how to send 8 channels data from one loop to other for processing (base band FFT N channels) at 51,2KHz ???

Please I need help !!!

07-09-2014 07:42 AM - edited 07-09-2014 07:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What is your DMA Fifo config ?

FPGA - <NumberofElements>

RT - <NumberofElements>

What is your RT Fifo config?

- elements in array (block size)

- size (block count)

Tasks

RT timecritical

- read the data

- write blocks to a RT Fifo

RT non timecritical

- read blocks from RT Fifo

- flatten to string

- write sgl element (block) to stream

Describe your Fifo structure...

07-09-2014 09:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi christian ,

Thanks for your reply, my DMA fifo config :

Type: target to host

Requested number of elements: 4095

data type: U32

channels count : 8

RT side :

I'm using rwvm Read (poly).vi to read 8 channels SGL waveforms at 51;2Khz and number of sampels to read is 5120 . I multiply this number by 20 to increase the buffer size on RT code to avoid DMA overflow. Please see attachments.

Thanks !!!

07-10-2014 04:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

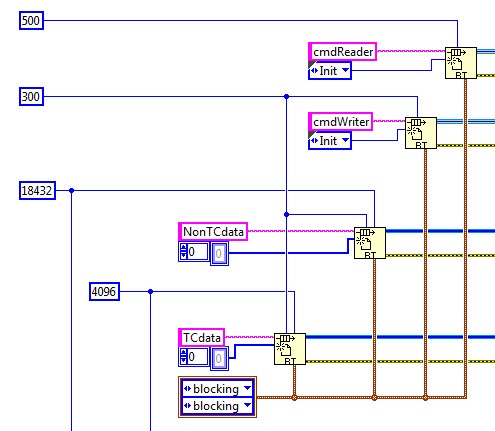

DMA Fifo:

To avoid overflow you have to configure the RT side which has a default size of 10000 (Rio4.0 and above 2^14 elements) or doubled FPGA depth (fifo_config)

RT Fifo:

config example

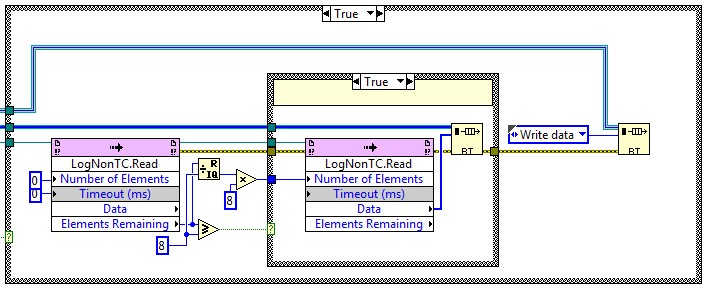

Read data from DMA to RT Fifo

(read all elements available and write this data block to your RT fifo, which is configured to hold n-Blocks of size x, i.e. 300Blocks of 18432elements each)

--> here I suggest to read a multiple of 8, because of your channel count

Read data from RT fifo to stream

(send data blocks to the host where each block is one element in terms of streaming buffer --> configure streaming buffer)

Configuring large RT Fifo's has an impact on memory usage, so have an eye on it.

Screens are just examples (not functional code)

Hope it helps

Christian

07-10-2014 10:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks you very much Christian but I think my real problem is the periode of time taken for processing data comming from fifo read. so the problem is that when I tried to compute FFT magnitude spectrum of this 8 channels simultanously (this is my goal) the consumer loop which has afifo read inside can't follow the fifo write one on consumer because it is very fast . For example I have in 100ms I have 10 blocks writen in FIFO but only one block can be processed in that time so after a certain periode of time the fifo will certainly overflow even with a huge configured size. So the problem I think is how to compute FFT of 8 channels simultanously with data comming from fifo read without affecting fifo write ?

07-10-2014 05:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've not done much with FPGA, but I've done a fair amount with PXIs. My "rule of thumb" is to use RT FIFOs to get the data out of the Time-Critical (Real-Time) loop and into a "Processing" Loop. Since the FIFOs are designed to be really fast, but not necessarily good for buffering, my Processing Loop generally immediately stuffs the data from the FIFO into a Queue (generally "large enough", but finite, so I don't have to worry about memory allocation or other time-consuming issues) (and, if I'm really feeling confident and want maximum speed, I use Lossy Enqueue, which doesn't block on writing).

My third loop dequeues the data "as fast as it can" and does stuff with it, such as sending to the Host via Network Streams, or potentially doing computations (FFT, etc.). You need to be sure that the rate at which you process is greater than the rate at which you acquire or you will miss processing some data. Note that using a Queue gives you a little buffering flexibility -- some steps might be slower than the acquisition rate, but if they are matched by steps that are much faster, you still win.

Bob Schor

07-11-2014 01:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If your RT is too slow try to implement the FFT on the FPGA. There are many examples available (FFT FPGA)