- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to set FPGA global variable value from host PC

Solved!07-18-2017 03:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

I have a VI running on an FPGA target in which I am using global variables to avoid having front-panel arrays (and thus reduce resource utilization).

The global variables are 1D arrays of FXP numbers that are static during the run of the FPGA VI, but should be able to be programmatically updated by transferring data from the host PC.

I can't figure out how to send the programmatically generated values from the host PC to the FPGA VI's global variables.

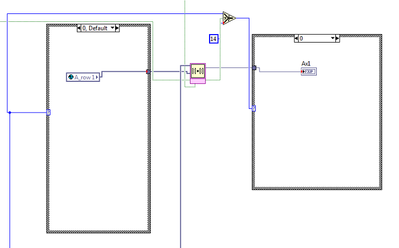

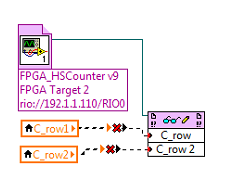

Since it's just a one-time data transfer of a relatively small amount of data (~200 elements across ~40 arrays), a Read/Write control seems like the tool for the job. But, the Read/Write Control with the FPGA VI as the reference can only access the frontpanel elements, not the global variables that do not appear on the frontpanel. (In the below pic, C_row and C_row 2 are global variables that do not appear on the frontpanel.)

If I instead use a reference to the global variable, I get an error on the host PC saying that the VI associated with the global variable is not compiled, but it doesn't seem like elements can't be compiled or have a build specification created. (The FPGA VI is currently successfully compiled.)

How can I do a "one-time update" to send data on the host VI to the FPGA global variables without creating frontpanel elements?

Select VIs attached.

Thanks in advance!

Solved! Go to Solution.

07-19-2017 01:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi phototrope,

you cannot access the FPGA global variable directly from RT host.

That being said you need to program a different way to send data from RT to FPGA!

Usual methods include:

- FIFOs

- accessing FP controls of the FPGA: when the global is an array of values you need atleast an index and a "new value" control on your FPGA. The RT sets index and new value and the FPGA is copying those data from FP control to your global…

07-19-2017 06:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Use a DMA FIFO to transfer the data and then the FPGA can set the global variable values.

For VIs larger than a few items, avoid front panel controls like the plague. They will eat up your fabric.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

07-19-2017 02:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks crossrulz. DMA FIFOs are the way to go.

After reading up on it, the only target/host data transfer methods the FPGA in my cRIO-9030 supports are (1) Read/Write Control and (2) DMA FIFOs. Memory items are purely target-scoped.

For those who have the same question as me, I'll explain it how I understand it:

(1) You can use Read/Write Controls on a Host VI to directly read and write frontpanel elements of an FPGA VI. This is pretty straightforward, kind of works as "sample on demand." However, it requires you to have a frontpanel element for each variable that you might want to read or write, which means the FPGA will expend extra resources on the buffer for those frontpanel elements.

or,

(2) You can use DMA FIFOs. The FPGA target can read data from a FIFO and store it in any kind of variable, including global variables (which do not appear on the frontpanel and are thus not accessible from a Read/Write Control.)

To transfer data from the Host VI to the FPGA VI, you need a Host-to-Target DMA FIFO. (To transfer data from the FPGA to the Host, you need a Target-to-Host.)

You can then create a VI on the Host that uses an FPGA reference to write data to the FIFOs, which will then can be read and loaded into a global variable upon run on the FPGA VI.

Note that the host only will "see" FPGA FIFOs that are included in the compilation bitfile, so if you have created a FIFO but you have not placed it into your FPGA VI, the host will throw an "Object does not exist" error.

Now I've just got to whittle down resource usage to be able to fit all that stuff on my target....!