- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FXP division by 2 fails

08-29-2013 05:51 PM - edited 08-29-2013 06:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

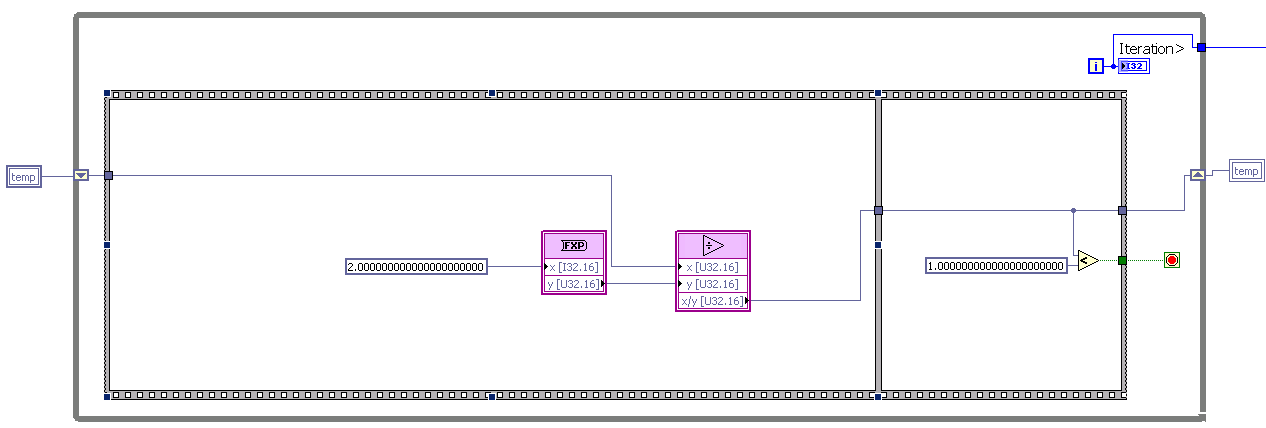

I simply want to divide an FXP number by 2 in my FPGA target but I get an incorrect result. For example when the input is 1.413788, out comes 0.206894 after one iteration. The code looks like this:

Using Labview 8.6 and the FPGA is a PCI-7833R. Please help me!

08-29-2013 07:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What's the point of converting from a fixed-point to a fixed-point?

If you get rid of everything except the math operations - no while loop, no sequence structure (which is unnecessary anyway) - what happens? I built a simple FPGA VI (LabVIEW 2012) that just does the fixed-point conversion and the divide, and ran it on my development computer (I don't know if 8.6 supports this mode). It works exactly as expected.

For dividing by 2, it would be a lot easier to either shift 1 bit, or reinterpret the same bit pattern such that the integer portion is 1 bit less, depending on which is appropriate for your application.

08-29-2013 08:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Are you sure about the input? If the input were O.413788, the answer would be correct.

Mike...

Certified Professional Instructor

Certified LabVIEW Architect

LabVIEW Champion

"... after all, He's not a tame lion..."

For help with grief and grieving.

08-30-2013 01:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

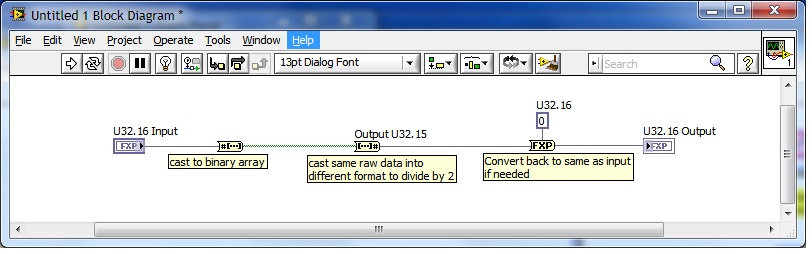

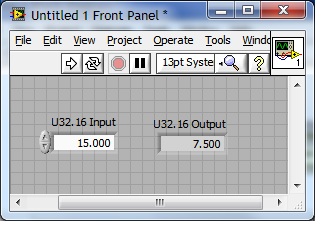

Fixed point divide by 2 can be done just by changing the representation.

This works for any divide by a power of 2, IE 2, 4, 8, 16, 32.......

This method uses no fabric and if inside a SCTL uses not clock cycles.

08-30-2013 01:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@fppf wrote:

Fixed point divide by 2 can be done just by changing the representation.

There's no need to use so many functions to do this. The simplest way to do this is the Reinterpret Number function, although I don't know if it was available in LabVIEW 8.6. Of course since the functions you suggested use no FPGA fabric, this isn't an efficiency concern, but I think fewer functions makes for cleaner code.

08-30-2013 01:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Check the format of your fixed-point value. Make sure you have the binary point set properly as well as the interger bits and sign bit. You make be losing the integer part apon conversion.