- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA with unsynchronized data transfer to host.

03-11-2014 11:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I have a question about synchronizing my FPGA application and my Host.

I am using a 7962R Virtex5 board and a Ni5323 digitizer (80MHz).

To start my application i am triggering the acquisition with a 50kHz trigger on a PFI line.

It does work but when i take the data out of the FIFO on the host i can't see a stable waveform on the graph.

I am acquiring 1024 points and have the host FIFO depth at 500000.

Does anyone have an idea since i thought that DMA transfer is inherently synchronized?

I attached my fpga and host code if that helps.

Thanks

03-12-2014 06:30 PM - edited 03-12-2014 06:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Basbee,

I see a main fundamental flaw in your current setup. When using Analog inputs or outputs with FlexRIO, it is a must that the SCTL (Single Cycle Timed Loop) and ADCs on the FAM are driven by the same clock. You were right in the idea that we want the SCTL running at 80 MHz, but we need to actually use IO Module Clock to time the SCTL so that is the same 80 MHz clock that is driving the ADCs and not a separate clock that just happens to be the same frequency.

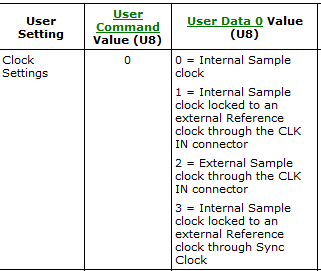

For the record, you change what is on IO Mod Clock 1 in the CLIP, as shown below (You want it -0 for 80 MHz):

Then, the only other thing I would point out is that the FPGA is acquiring 1024 points, but your host VI is reading 1024*10 samples that it graphs. I would imagine there would be jumps in your data at those points considering you are sampling every 20uS (based on your trigger) and each time you sample you collect (12.8uS of data).

Cheers,

03-12-2014 07:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Chris,

Thanks for the reply.

I am actually using the IO module clock i just forgot to change it. And for the 10 times 1024 samples. Even if i take out only 1024 samples at a time the jumps happen.

03-13-2014 01:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Problem solved, the host depth was not big enough. i have to set it to 900Mpoints to get it stable.

I am not sure if that is the right approach but it works.

I have another problem. When i run the acquisition, i can see the spectrum or multiple ones on the waveform graph.If i stop it and start it again it will shift a little as if there are still points in the FIFO which not have gotten out.

I am using a reset method node before i close the fpga reference because i thought that makes sure that the DMA FIFO is empty.

Am i understanding that right?

Cheers

03-13-2014 03:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You can do a zero-element read from the FIFO to return the number of elements remaining in the FIFO, then read that number of elements with another read. This effectively empties the FIFO.

CLA

03-13-2014 04:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Thoult,

Thanks it works. I put that in Front of my acquisition loop and now my spectra always start at zero.

I just don't know why the reset and stop method node don't work too.

Cheers

03-14-2014 03:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I don't believe the reset method is applicable to DMA FIFOs. Stop should work though (although I always use the zero element read anyway, out of habit).

CLA

03-14-2014 01:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Basbee wrote:

I just don't know why the reset and stop method node don't work too.

It's an older post, and I've never confirmed it, but this thread says that the Stop method of a DMA FIFO only clears the host portion of the FIFO which could leave stale data in the FPGA memory, perhaps that's what you're seeing?

03-14-2014 05:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear nathand,

Thanks for that. I thought I read something that it clears the DMA and i assumed that it works for both sides but i guess i was mistaken. Do you know if there is a way to make sure it is clear with a method node on the FPGA side. Because the clear method node only works for target scoped FIFOs and not DMA ones.

If not the other method works fine.

03-14-2014 05:56 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

There is no way to clear it on the FPGA, you need to read the data on the host until there's no data remaining.