- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA digial output problems with while loops on 7951 w/6581

03-13-2014 10:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Im trying to simply output 4 synchronized square waves from a digital output port. I have the block diagram pictured in the attachment running on my FPGA. A loop on my controller simply updates the value of "rate mode frequency" to change the rate and the direction boolean changes the phase of the square waves. I had this working fine on a PXI-7833R. No problems at all, and was able to generate the signal up to several MHz.

I had to switch to a PXI 7951 with the 6581 Digital I/O attachment, and I cant get the digital outputs to work. I can see the boolean values changing if I attach an indicator to the lines going into the I/O control, but I see nothing on the scope.

The 7951/6581 isn't broken, I can see digital output values changing if I write a very simple code using a for loop and update values that way.

Ive been trying to fix this the past two weeks and have gotten nowhere, so hopefully someone here will have some insight to the problem.

Thanks in advance,

-Mike

03-14-2014 09:41 AM - edited 03-14-2014 09:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi M1080,

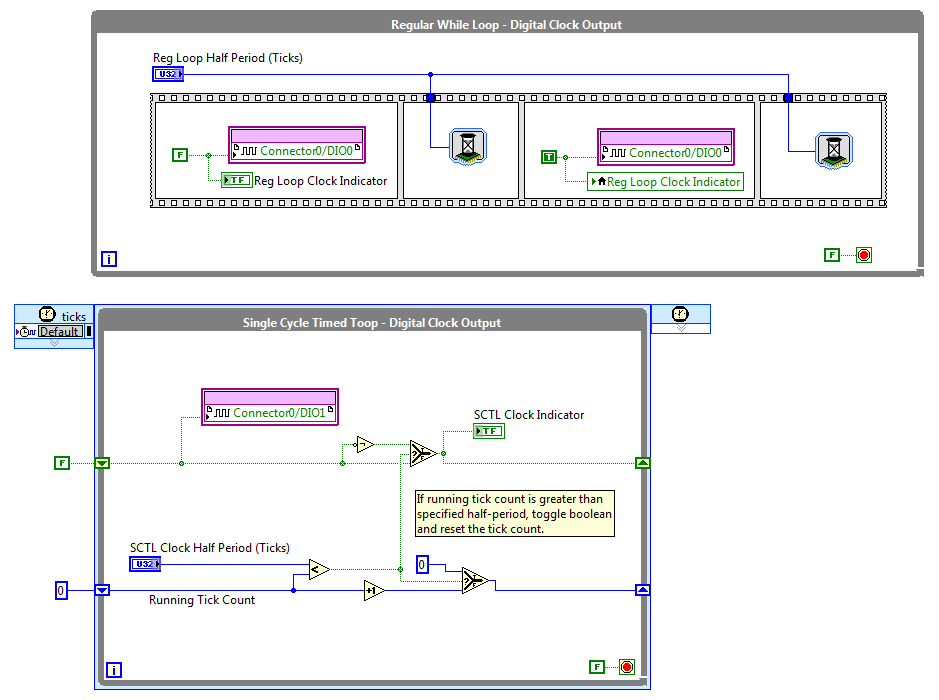

I'm not sure why the code you posted is not behaving as you expect, but it may have something to do with the architecture. Is there a particular reason you are using the square wave generation express VI? Typically that function is intended for analog values, and the way that you are converting the output to booleans in another loop seems a bit inefficient to simply generate a clock. I would recommend directly toggling a boolean line after a specified number of clock ticks. The attached image illustrates two possible ways to approach this:

Cheers!

03-17-2014 01:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Kevin,

Thanks for the reply. I tried the block diagrams you posted, and Im having the same problem. If I use a while loop , like is in the diagram you posted, It doesn't work. I see nothing on the oscilliscope, but I do see the values changing on the "Reg loop clock indicator".

If I simply change the while loop to a for loop, it works, and I see the square wave on the scope.

03-17-2014 02:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Mike,

Have you gone through the Getting Results with the NI PXI-6581R manual? There are alot of extraneous variables that going through a getting started example will help eliminate. Would you be able to go through this manual and post which step you got stuck on?

03-19-2014 03:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I figured it out...

For some reason, in a while loop, I have to set the port WE to true every time I write the digital channel. In the for loop I dont have to do this.

03-19-2014 05:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for posting your solution. If you're curious why thats required you may find the help document below interesting. I've posted the portion of interest from the document.

Using FPGA I/O (FPGA Module)

http://zone.ni.com/reference/en-XX/help/371599H-01/lvfpgaconcepts/performing_basic_i_o/