- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Tidbit: More flexible testing of DMA Inputs / Outputs

01-06-2017 07:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

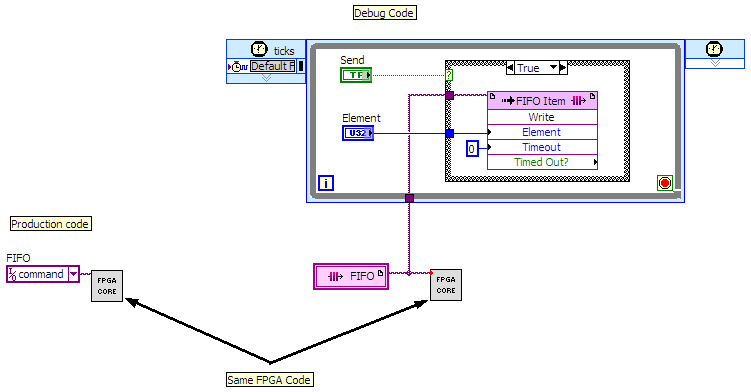

Whenever I need to test some FPGA code, I tend to write debug VIs which include user interface items so that I can do some interactive testing in simulation mode (where timing violations are no problem 🙂 ). Whenever I have a DMA as a main input for my code, this option has proven unwieldly. I would end up copying the majority of my FPGA code into a new VI, replacing the DMA input (or output) with whatever custom code I wanted to use for testing. This often led to problems when I had finished debugging in simulation mode, having to copy the code back and re-link with the DMAs. That was until I recently realised something.

Instead of hard-wiring a DMA Input (Host to Target) or DMA Output (Target to Host) into your main FPGA code, wire up an appropriate FIFO Control instead. Put a control for the FIFO on your FP and set it to only include the Read or Write interfaces as required. You can richt-click the left-top terminal of the DMA Read ior Write and simply choose "Create Control" to have it set with the correct parameters.

Then, in a wrapper top-level VI you can simply wire in the DMA (which is hard-coded into your project) and things work as usual. The benefit is that you can now actually wire in a normal FIFO woth both Read and Write ports and use whatever UI elements you like to fill the FIFIO with data. The sub-VI containing all the FPGA logic IS THE SAME. There is no longer any copying between production versions and debug versions of essentially the same code.

The same can be done for Target to Host DMAs, just make sure to set the Read and Write options of the controls accordingly.

If resources allow, you might even be able to compile the Debug version and do some testing directly on hardware. My Debug UIs contain over 100 controls. Each command being sent then packs the data into a common format (U64 in my case) which is then unpacked in the FPGA core for usage. As such, my UI in simulation mode also takes care of ensuring that the packing / unapacking of the parameters for DMA transfer is being performed correctly.

01-22-2017 06:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I recently demonstrated the Desktop Execution Node which can be used to provide inputs and acquire outputs from the FPGA. When simulating, random data is generated from IO. This is not the case with the Desktop Execution Node, you can execute your FPGA code without modifying it and from a Host PC be pushing the data you would normally expect from your Inputs. I have included some documentation on this below:

http://www.ni.com/white-paper/51859/en/

http://zone.ni.com/reference/en-XX/help/371599M-01/lvfpgahelp/using_desktop_execution_node/

Best regards,

Ed

01-24-2017 04:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hmm, so the Desktop Execution node is similar to simulation mode where CLIP IO nodes can be set / read directly? This is of course available already by specifying a simulation VI, but the desktop execution node seems to abstract this to a much more useful level.

Why does NI not explain explicitly that this is deveoped on top of the existing CLIP interfacing methodology so that those of use used to making use of the old technologies might actually have a look at this new possibility? I personally would never have made the bridge between the old CLIP VI method and the "Desktop Execution Node"......

01-24-2017 05:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Intaris,

As of 2014 we updated our FPGA and Real Time training to be the Embedded Control and Monitoring course. New features and concepts such as the Desktop Execution Node are discussed and the Desktop Execution Node is even demonstrated.

As provided we also have white papers on this, there are many examples in the Example Finder if you search Desktop Execution on how to use the node. Additionally with each release of the FPGA module, the download page for such release has a section called features which describes the additional new features added as demonstrated in the below link:

http://www.ni.com/download/labview-fpga-module-2014/4827/en/

What other documentation would you like and I may be able to file a documentation CAR on this?

Best regards,

Ed