- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Configuring of FPGA references

06-12-2014 06:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone,

We have a large number of cRIO chassis, all having the same controller code. This controller code opens a dynamic FPGA reference using the Open FPGA VI Reference function. The FPGA code for every cRIO is different, but all have the same front panel. To build the code for a particular cRIO chassis, we manually configure the Open FPGA VI Reference function and proceed with the build. This works fine, but we would like to automate the build process for all the cRIO chassis, and our attempts have not been successful.

We have tried several approaches:

1) Using a subVI having a case structure, where each case has an Open FPGA VI Reference function pointed to a particular FPGA VI. We run out of memory when compiling with this approach.

2) Dynamically calling a VI that contains an Open FPGA VI Reference function pointed to a particular FPGA VI. However, we get Error 1124 (VI not compiled for OS), even though the FPGA VI is under the cRIO in the project.

3) Changing how the Open FPGA VI Reference function is configured doesn't resolve the issue. We have tried VI and Bitfile, but not Build Specification.

We are using LabVIEW 2012. I understand that in LabVIEW 2013 there is the Open Dynamic Bitfile Reference function, which might resolve the issue, but we are not allowed to upgrade to LV2013.

Does anyone have any ideas on how to automate the selection of which FPGA reference is opened?

Thank you in advance for your assistance.

Kind Regards,

Chris

06-13-2014 01:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

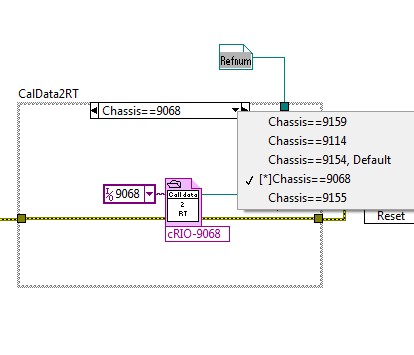

I suggest to use Conditional Disable Symbols on the project level. My example shows the selection of a bitfile by the created symbol 'Chassis'. For the resource names I use aliases set in the MAX on device (RIO0) level.

Hope it helps

Christian

06-16-2014 11:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Another option might be to use the approach of putting the Open nodes in subvis but instead of calling them dynamically put them in a case structure and mark them as "load when called" so hopefully the out-of-memory exception will go away.

06-16-2014 02:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

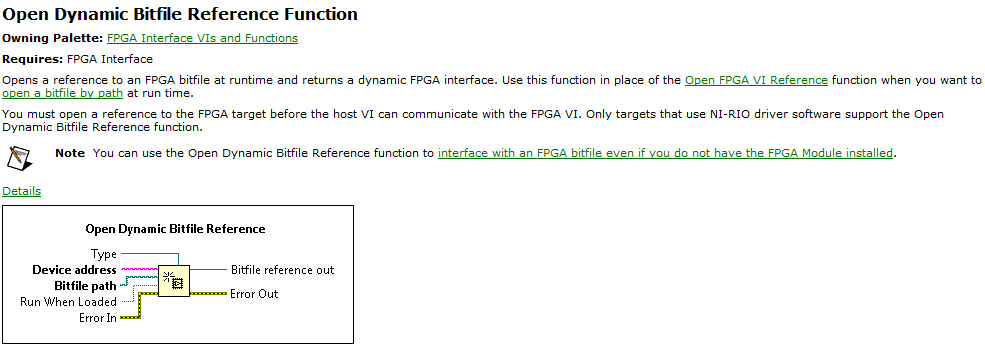

Can you use the "Open Dynamic Bitfile Reference" Function? At runtime, the RT system can call it with a path to a bitfile, and that bitfile will then be loaded into the FPGA and executed. As long as all the FPGA/RT interfaces are the same for the various bitfiles then I think it should work.

Note that if you also have a bitfile setup in the FPGA flash memory for immediate launch whenever the FPGA first receives power, it will start running when the cRIO starts and later be replaced by the one the RT system is using when the RT system finally gets around to shoving its copy into the FPGA.

06-16-2014 02:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Open Dynamic Bitfile Reference would be a great solution, but it is a LabVIEW FPGA 2013 feature and the original author noted they were not able to upgrade to 2013.

06-16-2014 03:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

christian_w,

Thank you for your suggestion. It works quite well, and I no longer have the insufficient memory issue. However, there is unexpected behavior. If I first do a build of each of the FPGA VIs, and then change the value of the Conditional Disable in the Project to switch between which FPGA code is used, then I am required to re-build that particular FPGA code. It seems quite odd, and I don't understand it. Do you (or anyone else out there) have any thoughts on why this might occur?

Kind Regards,

Chris

06-17-2014 03:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It seems that you use a VI reference in the ConfigureOpenFPGAReference dialog. Try to use a bitfile reference. This should work.

06-17-2014 10:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm currently using a bitfile reference when this problem of requiring a re-build occurs. I'll try the other 2 options and see what happens.