From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

05-17-2013 11:54 AM

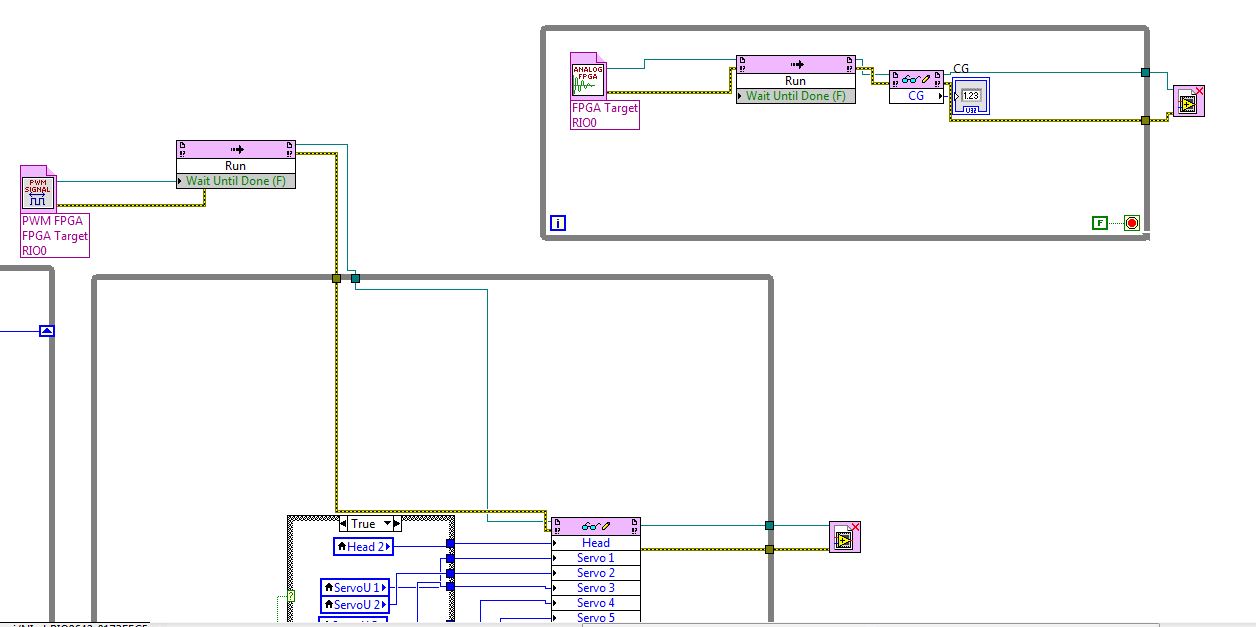

Im using an sbRIO and I have 2 FPGA in it. I program both to open in real time. FPGA 1 is regarding getting data from analog signal and FPGA 2 is sending PWM. If these 2 are seperated, I have no problem opening them in real time. When I combine them together in a single real time VI, only FPGA 2 is working. FPGA 1, which supposedly shows values in charts is just totally empty!

Question is, how do I integrate both FPGAs in a single real time VI? Will combining the codes in FPGA screw up the timing?

05-19-2013 08:11 AM - edited 05-19-2013 08:11 AM

Hi Augustg

How exactly are you combining them?

Are they just separate while loops that you run in parallel, or is there some data dependency that stops one of the processes running.

Also, are both the FPGA VIs trying to access the same hardware resource?

Might be worth posting your code so we can all see.

Kind regards,

05-19-2013 08:24 PM

im using sbrio. there are 2 fpga vi under the fpga tab. im trying to open them both at once in a single realtime vi using2 open/close reference.

05-19-2013 08:40 PM

I'm pretty sure the sbRIO cards only have 1 FPGA on them. So when you load the second FPGA code, the first is being overwritten. You need to make a single FPGA VI that can handle both functions. If you post your code, we can give more detailed advice.

05-20-2013 06:58 PM

05-20-2013 08:04 PM

But the FPGA target can only have 1 load at a time. You either need to complete your operations of one load and then load the next or you need to combine the functionalities into a single FPGA.