- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[Bug] FPGA VI-Defined Memory node producing erroneous errors

09-15-2014 07:26 AM - edited 09-15-2014 07:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I just run across a LV bug in checking the functionality of a VI-Defined Block Memory node.

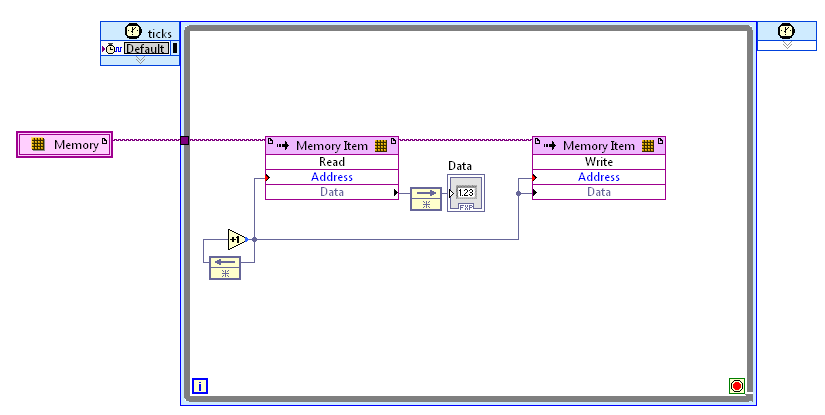

When utilising this function, it is seemingly invalid to propagate the memory block Reference from one node to another. In the example shown below, the code will not compile. If we fork the reference coming from the VI-defined node and connect "directly" to the read and write nodes, it will compile no problem.

To add insult to injury, wiring up the nodes int he OPPOSITE direction (First write and then read) things compile fine, just don't try wiring up the output of the Read node to anything..... The node which complains is the "Read" node by the way which is convinced there is no feedback node attached. Again seemingly no logic to this at all.

I don't see any logic in this differentiation, therefore I am tempted to label it a bug.

Shane.

PS, This is in LV 2012 SP1, sorry. I forgot to mention that.

- Tags:

- fpga