- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

2012 SP1 FPGA compile worker error

05-16-2013 05:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

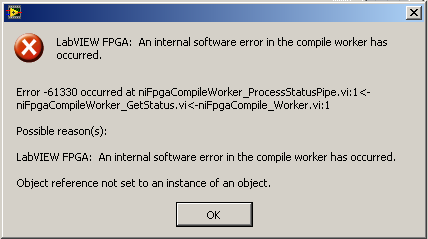

Picture says it all really.

It's an FPGA project with a Socketed CLIP and some external clocks from CLIP. It seems to compile on the second attempt, just doesn't work *quite" properly. The first compilation attempt yields the error shown above on several different machines.

Shane

05-17-2013 01:46 AM - edited 05-17-2013 02:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

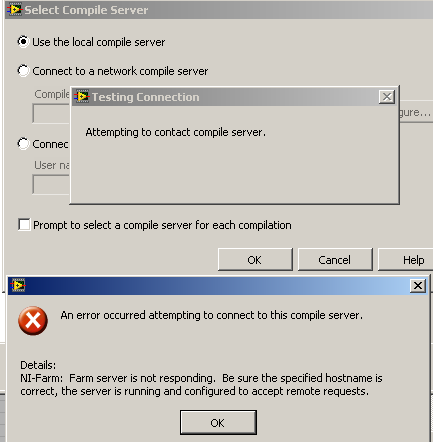

I tried compiling the code again last night on my home PC and it got part of the way through before complaining about a communication error with the compile worker. If I tried starting the compilation without closing and re-opening the VI in question it then complained that the compile farm was not responding. We don't HAVE a compile farm and I have never chosen to use a compile farm but regardless of which compile option I choose at the start of compilation, it continues to complain about communication problems with the compile farm.

We jsut upgraded to 2012 SP1 as we had previously been able to compile. One of our partners had to make a change to a CLIP module and after re-incorporating those changes into our project, the compilation process seems really shaky.

Please note that the exact same code compiles fine in LV 2011 SP1 (different Xilinx compiler version of course).

Shane.

05-17-2013 02:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Oh and another perhaps useful piece of information....

Regarding my first post, when starting the compilation a second time, it asks to save a global variable file which really should have been saved the first time. Maybe the missed save was the reason for the first error? Could this be a parsing error?

05-17-2013 03:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ah, maybe it's related to THIS PROBLEM.

I DO have indicators in a conditional disable structure which is actually disabled (but the indicators are still ont he FP).

I'll try re-activating them and see if the problems go away.

Shane

05-21-2013 05:07 AM - edited 05-21-2013 05:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

OK, this is getting very annoying.

I am now having trouble importing vhd files into a CLIP definition for our FPGA target. Whenever I copy in new vhd files (supplied by an external partner) I only get as far as the Syntax Check on page 3 of the import wizard where the syntax check returns an erorr (-61499). I've searched on the topic and the only links I found were clockes over 400MHz (We're not using those) and corrupt DLLs which I should delete from myy user directory (Which I have failed to find beyond the ones int he Xilinx folder itself).

Here's the returned text:

Time Resolution for simulation is 1ps. Waiting for 8 sub-compilation(s) to finish... Compiled 20 VHDL Units Built simulation executable x.exe Fuse Memory Usage: 82680 KB Fuse CPU Usage: 890 ms Error -61499 occurred at niFpgaIPINodeGetDllError.vi:1<-niFpgaIPINodeGetPortsInfo.vi:1<-niFPGA_ClipGenerator_DoFuse.vi<-niFPGA_ClipGenerator_WizardPage3.vi Possible reason(s): LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support at ni.com/support. Additional Information: Failed to call Windows API. If this error persists, contact National Instruments technical support. C:\Program Files\National Instruments\LabVIEW 2012\vi.lib\rvi\IPIntegrationNode\IPINode_Dialog\niFpgaIPINodeGetPortsInfo.vi

I'm using LV 2012 SP1 on Win7 64-bit (32-bit LabVIEW).

This internal error is making my life extremely difficult as I'm in a constant spin as to whether I have the newest vhd definition s incorporated in my project or not. What happens if I continue despite this error during syntax chaek?

Shane

05-21-2013 09:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Seems like I can get past this now by reverting my project filr to the one in our source control.

Still the whole FPGA experience with 2012 SP1 seems very fragile to me. Or maybe 2011 SP1 was a golden version (like 7.1 for LabVIEW itself) and I'm spoiled.....