View Ideas...

Labels

Idea Statuses

- New 2,936

- In Development 0

- In Beta 1

- Declined 2,616

- Duplicate 698

- Completed 323

- Already Implemented 111

- Archived 0

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Enabling use Labview FPGA front panel in interactive mode without recompilation-

Submitted by

andrewsi

on

05-31-2012

05:24 PM

4 Comments (4 New)

andrewsi

on

05-31-2012

05:24 PM

4 Comments (4 New)

Status:

Declined

Technically, I suppose you could consider this a bug.

The situation is this:

- You develop an FPGA module for an sbRIO, cRIO, or what have you.

- You share the compiled code and .lvbitx with a team member, who needs to run that front panel in interactive mode, however, his sbRIO lives at a different IP address.

- The only change he makes to the product is to right click on the target in Project Explorer, so as to be able to change the expected IP address. However, the target hardware is otherwise completely identical.

Net result:

- The co-worker has to wait for a complete recompilation of the bitfile, which can be an hour or more in the case of a complex design. There's no reason why the user shouldn't be able to completely re-use the existing bitfile just to send it to a different IP address.

Perhaps there's some technique I'm missing, but this is causing our team a pretty significant loss in productivity. (Note that we have no issue with re-using the .lvbitx from RT host code, that works just fine - it's using an existing front panel in interactive mode that you can't do without recompiling it locally.)

Project Explorer:

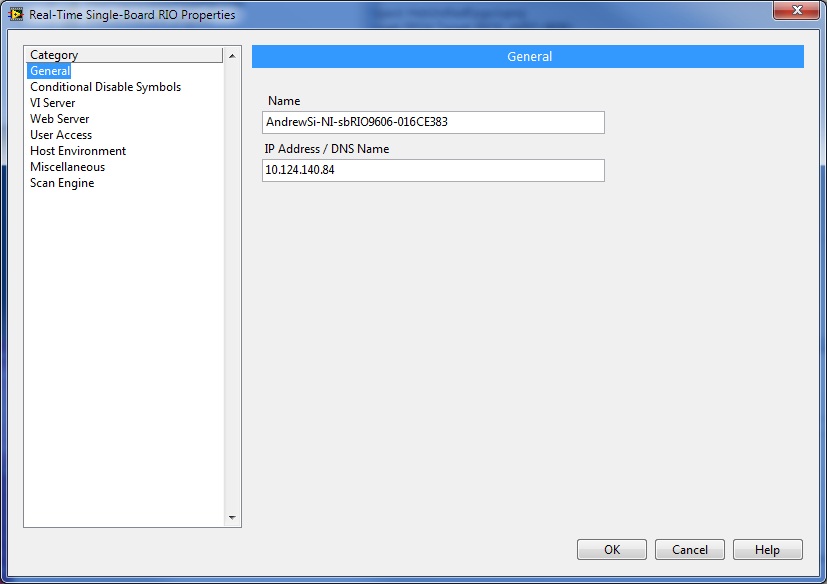

Change the target IP address:

Now you have to recompile...

Labels:

- Tags:

- fpga

4 Comments

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.

Any idea that has received less than 6 kudos within 6 years after posting will be automatically declined.