View Ideas...

Active

Inactive

Inactive

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

64 bit FPGA tick-counter

Submitted by

MarcoMauri

on

06-16-2010

05:20 AM

3 Comments (3 New)

MarcoMauri

on

06-16-2010

05:20 AM

3 Comments (3 New)

Status:

New

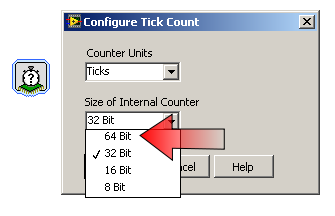

The Tick Count function in LabVIEW FPGA can represent time periods with tick count accuracy of up to 2^32 clock cycles, that is (using the standard 40 MHz FPGA clock) about 107 seconds.

Sometimes I need to handle longer time spans, and I use this example.

I suggest to implement a built-in 64-bit tick counter.

Labels:

3 Comments

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.