- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

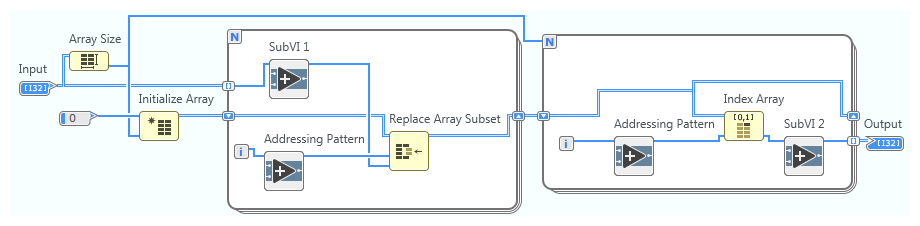

show me how can i make subVI 1 , subVI 2 and addressing pattern in this ping pong diagram

05-16-2017 05:16 PM - edited 05-16-2017 05:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It looks like you are trying to do this in an Optimized FPGA VI is that correct?

The SubVI1 and SubVI2 are your own custom code to operate on data that will be stored in your ping-pong array.

The addressing pattern is whatever logic you need to write into the replace array subset without ping-pong. It can be as simple as wiring up directly to 'i'.

Please note that if this is Optimized FPGA VI, you will need to have fixed size array on your controls and indicators.

05-17-2017 10:26 AM - edited 05-17-2017 10:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In Comms 2.0, you don't need to have a ping-pong logic in your algorithm. The latest FPGA compiler (Optimized FPGA IP compiler) can automatically figure out if any array in VI needs a dynamic memory management(i.e. ping-pong memory) to maximize the throughput performance and map the efficient memory implementation to those arrays.

In our old design document (http://www.ni.com/documentation/en/labview-comms/latest/fpgaip-prog/ping-pong-in-fpga-ip-vis/), you can have the optimal design even with VI not having a ping-pong logic (as shown in the attached picture)

- « Previous

-

- 1

- 2

- Next »