- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Main Simulation entity HLD IP from VIVADO HLS

04-18-2017 07:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Is there any documentation on .eip form for importing IP using HDL and IP-XACT .xml file?

04-19-2017 01:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Phy_comm,

I'll take a closer look at the examples you have. Also, were you able to get the HDL import examples projects included in LabVIEW Communications working?

04-19-2017 07:33 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes the examples are working. Even my codes are working but when there is single vhd file.

04-20-2017 07:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

An interesting thing is happening here.

04-20-2017 01:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Phy_comm,

Thanks for updating with those details. I'm still looking into it. While looking through your source files, I noticed that they appear to be generated in Vivado 2016.4. Is this correct? If so, would you be able to try generating the same files in version 2014.4? This is the version that LabVIEW Communications 2.0 uses. I'm not sure if that would be the direct issue, but it would help rule out any compatibility concerns.

04-20-2017 02:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I actually used Vivado HLS because it has necessary C++ libraries. Can it be issue?

Can you cite me example/procedure of how Labview Communication 2.0 uses VIVADO to generate IP?

I will generate IP accordingly so that there is no mismatch.

04-21-2017 07:31 AM - edited 04-21-2017 07:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi!

04-21-2017 10:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

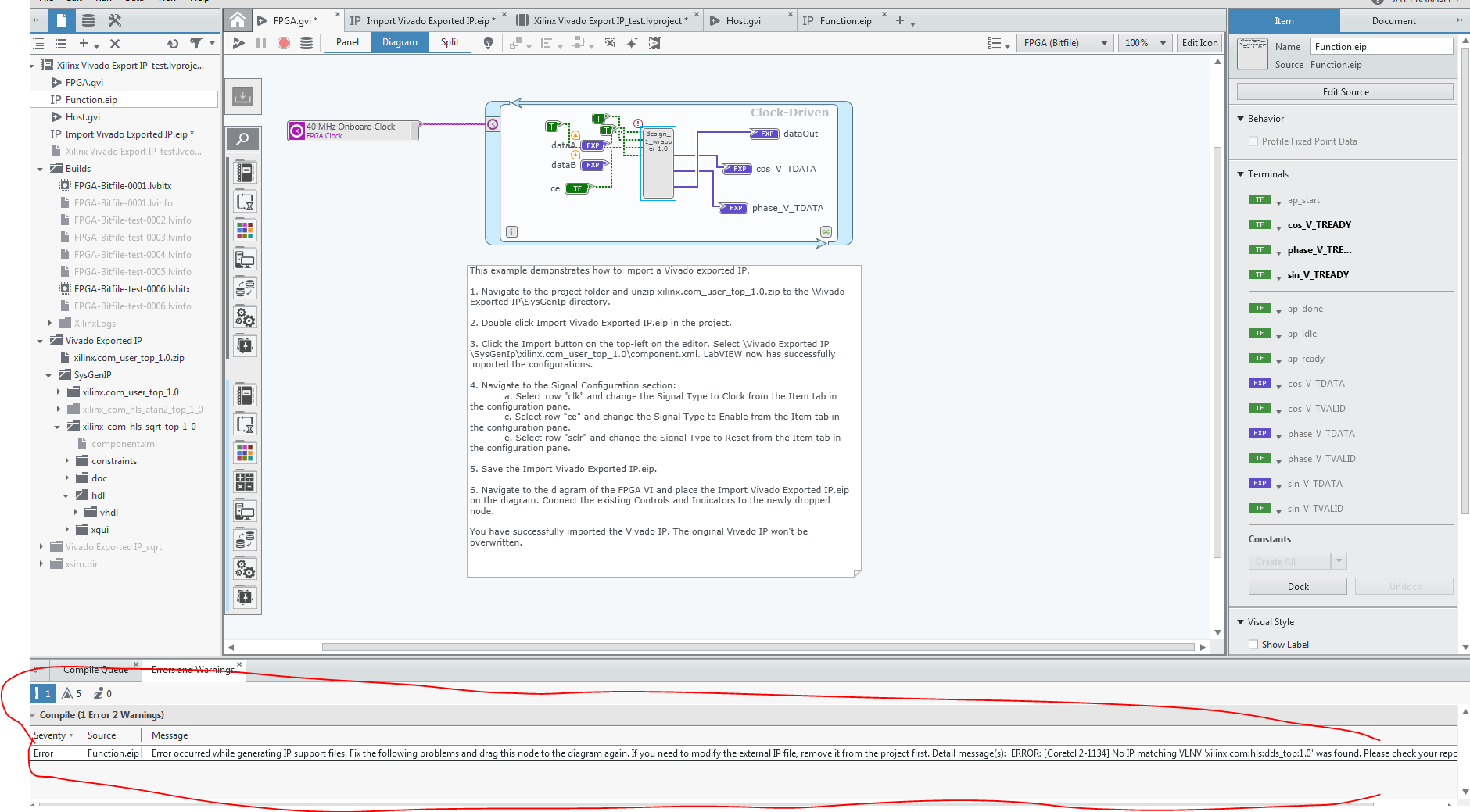

What I conclude till debugging now is that generating IP from VIVADO helps identify the HDL port correctly and there is no error in .eip file as previously. But when running FPGA it compile FPGA and returns error:

Error occurred while generating IP support files.

ERROR: [Coretcl 2-1134] No IP matching VLNV 'xilinx:com:hls:sqrt_top:1.0' was found.

The IP file is attached.

04-24-2017 02:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Phy_comm,

Thank you for the update. I will take a look at your latest source files.

We are still looking into this issue and will update you via the support channels when we have a suggestion with how to proceed.

Regards,

Kyle S.

04-25-2017 04:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi! Kyle!

Thanks for updates. I am eagerly waiting for leads. Meanwhile can you help me check if you can use the example of VIVADO IP to import and use IP generated from HLS or Vivado in FPGA diagram?

I guess that example itself contains an imported IP. It should be known how it was generated.

This would clear if any step is being missed.attached pdf has recommend steps