- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Ni5640R sync with external clock

03-23-2014 09:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I have a highly stable 10MHz sine source, and I need to phase-lock NI5640R's internal 200MHz generator to it.

I don't really understand half of the parameters in "Config Timebase". Any advice on how to do this?

03-24-2014 12:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi thu,

Can you post the project that you are using? Is this one of the sample projects for the 5640R?

Thanks,

David B.

National Instruments

Applications Engineer

03-24-2014 01:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm not really sure if I may post my project at the moment. In any case, any NI5640R project should do.

If you open any exaple, you'll see that in every NI5640R FPGA project, user must configure the timebase using the "Config Timebase" virtual instrument from NI5640R library. Timebase settings include configurations for external clock and PLL.

I just need some guidance on how to correctly set this VI's settings in such manner, that PLL would lock on external 10MHz signal, and phase-adjust the internal 200MHz oscillator in case it begins to drift.

03-25-2014 06:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi again,

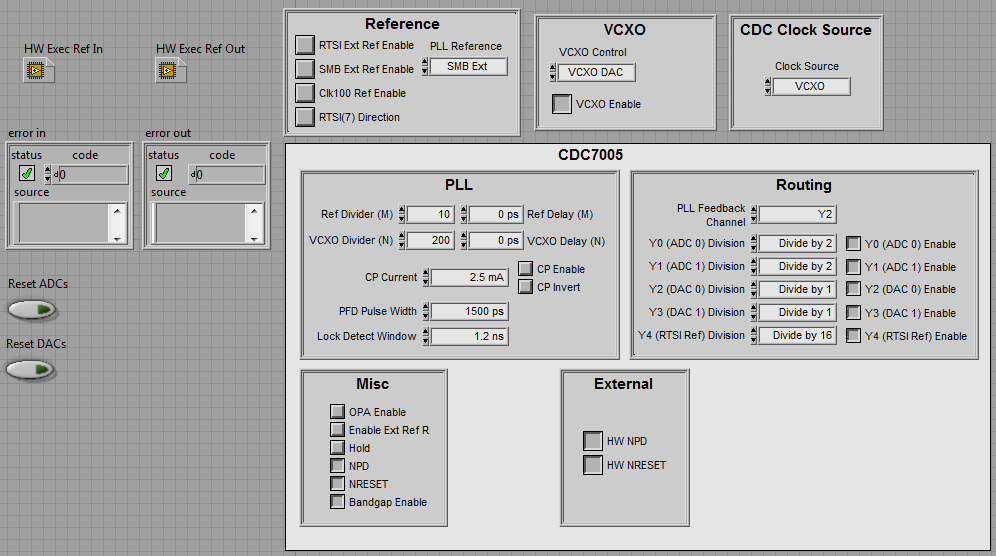

I looked through the VI, I believe all you need to do is set "PLL Reference" to SMB Ext, enable the "SMB Ext Ref Enable" property and set the PLL settings. The PLL settings are really up to you; if you're not sure what to set them to, I'd recommend leaving them at their defaults. Most of the VI's are just writing to registers onboard the device, I believe that these 3 are all you need to set.

Thanks,

David B.

National Instruments

Applications Engineer

04-01-2014 06:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

As I understand it, in:

CDC Clock Source tab:

* Clock Source = VCXO, since I need not external clock, but internal oscillator locked on external signal

VCXO tab:

* VCXO Control = PLL, since VCXO frequency will be controlled by external clock via PLL

* VCXO Enable = ON, obviously

Reference tab:

* RTSI Ext Ref Enable = OFF

* SMB Ext Ref Enable = ON, since this is the external signal source

* Clk100 Ref Enable = OFF

* RTSI(7) Direction = OFF, don't know what it is, but doesn't seem relevant

PLL tab:

* Ref Delay = 0ps, I only care about phase stability at the moment, so delay is not relevant

* VCXO Delay = 0ps, same here

* Ref Divider = 10, this divides 10MHz external reference to get 1MHz

* VCXO Divider = 200, this divides 200MHz internal generator to get 1MHz, then both 1MHz freq's are synchronized

* CP Current = 2.5mA, but I have no idea what this does

* CP Enable = NO, no idea

* CP Invert = NO, no idea

* PFD Pulse Width = 1500ps, (CDC7005 datasheet states, that PFD pulse is something that improves spurious suppression) I have no idea how wide the PFD pulse should be, I guess it depends on external source quality

* Lock Detect Window = 1.2ns, as I understand it, PLL is considered locked when rising edge of controlled signal of is in this window, so smaller window means less jitter

Routing tab:

* PLL Feedback Channel = Y2, this is by default, I don't know if this should be touched. This is also a bit confusing, since the choice is between [Y0, Y1, Y2, Y3, Y4, Y3, Y3, Y3]. I wonder how these Y3's are different?

* Y0 (ADC0) Division = divide by 2, Y0 Enable = YES, I see no need to modify this

* Y1 (ADC1) Division = divide by 2, Y1 Enable = YES, same here

* Y2 (DAC0) Division = divide by 2, Y2 Enable = YES, same here

* Y3 (DAC1) Division = divide by 2, Y3 Enable = YES, same here

* Y4 (RTSI Ref) Division = divide by 2, Y4 Enable = YES, same here

Misc tab:

* OPA Enable = FALSE, OPA is a enable/disable control for amplifier. I'm not really sure about what it does and if this is even connected in NI5640R, default is off

* Enable Ext Ref R = FALSE, may be something related to what I need, by default it is off

* Hold = FALSE, as I understand, when this is enabled, PLL tries to maintain lock when missing reference cycle, probably may be used for clock extraction from serial data stream. for this application it's not necessary

* NPD = TRUE, according to CDC7005 datasheet, NPD is asynchronous power down, and should be held high

* NRESET = TRUE, asynchronous reset signal, should be held high

* Bandgap Enable = TRUE, not sure what bandgap is, and I don't think it's relevant

External tab:

* HW NPD = TRUE, should be hardware power down

* HW NRESET = TRUE, hardware reset

05-17-2014 12:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi thu,

I was also facing the same problem. I was able to lock 5640R to external clock using driver-config-clock but i was unable to lock 5640R using FPGA timebase settinggs. Below are the setting of time-base that worked for me:-

1: PLL Reference = SMB Ext

2: SMB Ext Ref Enable = True

3: VCXO Control = PLL

4: CP Enable = True (To figure out the correct settings of this variable was difficult and it is not documented anywhere in NI-5640R documentation aswell)

Hope this helps

-Adeel

05-17-2014 12:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yep, I pretty much figured it out. Though I've found that PLL frequency floats like hell. I was trying to measure the jitter noise by feeding same signal as clock reference and input signal. When connected in such fashion, input signal phase should be stable. What I've observed is random +/-100Hz frequency shifts. So if you need the precise signal, it's better to use NI5640R in external clk mode than in PLL mode.

05-23-2014 10:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

But i have used PLL and i havent observed any noticable frequency drift.

1: Connect 10 MHZ signal in external-reference.

2: A 15 MHz sine wave was given to the AI-Input port.

3: For frequency-offset (locking accuracy) visualization, XY-Graph was used

iit was observed that output on the XYGraph was a stable "DOT" and it was not rotating.

If there is some freqnency offset in the signal then the stable "DOT" on XY-Graph is rotaing in circle and instead of "DOT" you

should observe a "circle".

As per my observation locking accuracy achieved was better than 1/20=0.05 Hz. (I am saying 0.05 Hz bcz the "Dot" was not static instead it completed 1-circle in almost 20 sec)

-Adeel