From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

06-01-2010 03:36 AM

Hi,

I am using NI PCI-5640R. Following FPGA Base Clocks are available to me:

(1) Configuration_Clk

(2) RTSI_Ref_Clk

(3) DAC_0_IQ_Clk

(4) DAC_1_IQ_Clk

(5) ADC_0_Port_A_Clk

(6) ADC_1_Port_A_Clk

Can anyone help me with brief descriptions of each clock? When these clocks are to be used?

Kindly send me some URL links where I can find details about the usage of these clocks?

Thanks and Regards,

Rashid

Solved! Go to Solution.

06-01-2010 11:43 AM

Hello Rashid,

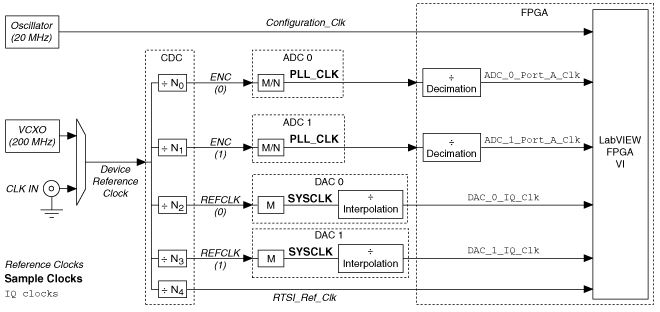

(1) Configuration_Clk - This is 20MHz onboard clock, which runs independently of the other clocks. The role of the 20MHz configuration_clk is to provide a fixed frequecny configuration clock that is use by STC2 ASCI for PCI-DMA operations. Also this clock is not synchronized to the 200MHz VCXO or to the external clock

(2) RTSI_Ref_Clk - This is a device reference clock derived from 200MHz internal VCXO, by setting the dividing factor ranging from 1,2,4,8 and 16.

The I/Q clocks are the signals that indicate the rate of the baseband data. These clocks indicate the rate of the data before the digital upconversion in DAC and the rate of the data after the digital downconversion for ADC. They are described as below.

(3) DAC_0_IQ_Clk and (4) DAC_1_IQ_Clk -

DAC_<i>_IQ_Clk = 2 × REFCLKDAC_<i> × Clock multiplierDAC_<i> / InterpolationDAC_<i>

where

REFCLKDAC_<i> is the specified device reference clock / N2 or 3 CDC. Specify the divisor using the ni5640R CDC Program VI.

Clock multiplierDAC_<i>(M) is equal to 1 or 4 ≤ M ≤ 20. Configure the clock multiplier using the ni5640R DAC Program VI.

InterpolationDAC_<i> is the hardware interpolation rate determined by the DAC fixed 4× interpolator times a programmable 2× to 63× CIC interpolating filter. The programmable CIC interpolator can be configured using the ni5640R DAC Profile VI.

(5) ADC_0_Port_A_Clk and (6) ADC_1_Port_A_Clk -

ADC_<i>_Port_A_Clk = ENCADC_<i> × Clock multiplierADC_<i> / (Predivide FactorADC_<i> × DecimationADC_<i>)

where

ENCADC_<i> is the device reference clock / N0 or 1 CDC. Specify the divisor using the ni5640R Configure Timebase VI.

Clock multiplierADC_<i>(M) is equal to 1 or 4 ≤ M ≤ 20. Configure the clock multiplier using the ni5640R Input Port VI.

Predivide FactorADC_<i> (N) is equal to 1, 2, 4, or 8. Configure the predivide factor using the ni5640R Input Port VI.

DecimationADC_<i> is the decimation factor for a particular channel in the ADC. Decimation is performed in various filters throughout the processing channel. Each channel includes one CIC filter (decimates by 1 to 32), two FIR-HB filters (each decimates by 2), one DRC filter (decimates by 1 to 16) and one CRCF filter (decimates by 1 to 16). Configure all these filters using the ni5640R ADC Configure DDC VI.

The figure below shows how all the above clocks are derived

Thanks

NI-khil

06-01-2010 11:45 PM