Benchmarking DMA Read Methods

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- CompactRIO|SingleBoardRIO

Hardware

- LabVIEW FPGA Module

- LabVIEW Real-Time Module

- LabVIEW

Software

Code and Documents

Attachment

Overview

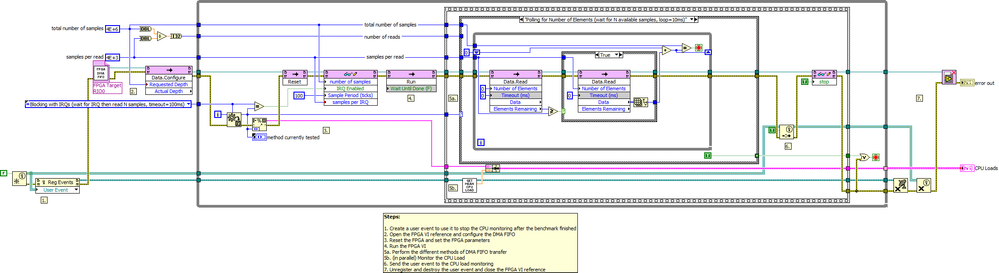

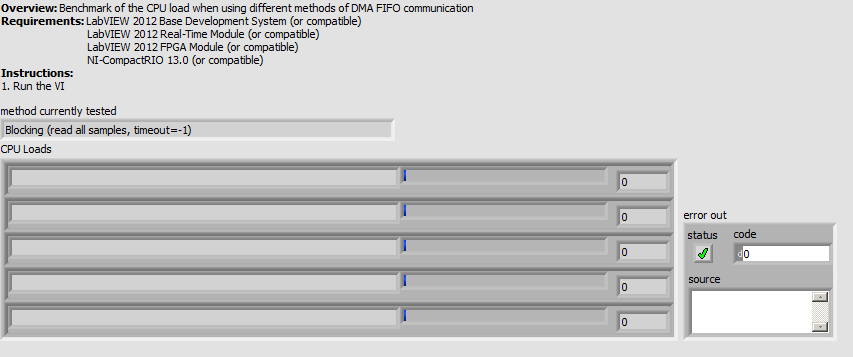

The example demonstrates benchmarks of the CPU load when using different methods of DMA FIFO communication.

Description

DMA FIFOs are an efficient method for streaming data from and to an FPGA. DMA stands for Direct Memory Access and DMA FIFOs are able to read/write data directly from/to the Real-Time's memory without causing too much load for the CPU.

In case the DMA FIFO transfers data from the FPGA to the Real-Time system, the data placed in the memory has to be read by the Real-Time application from the memory. For this operations there are several techniques to perform that tasks that differ in CPU load and whether the technique returns a fixed number of elements or a variable number of elements.

- Blocking

This technique has an infinite timeout waiting for a certain number of samples to become available. - Polling

This technique will read whatever elements are available at a fixed rate. - Polling with a Fixed Number of Elements

This technique specifies a timeout and the number of samples to wait for. - Blocking with IRQs

This technique uses an interrupt (IRQ) to synchronize with the FPGA. When the FPGA has written the desired number of elements to the DMA FIFO the FPGA triggers the IRQ. The Real-Time application waits on the IRQ and then read the FIFO knowing that the elements are available. - Polling for a Number of Elements

This technique periodically checks how many elements are in the queue. Only if there are at least the requested number of elements available the application reads the requested number of elements.

Requirements

Software

- LabVIEW 2012 Base Development System (or compatible)

- LabVIEW 2012 Real-Time Module (or compatible)

- LabVIEW 2012 FPGA Module (or compatible)

- NI-CompactRIO 13.0 (or compatible)

Hardware

- any NI FPGA hardware that supports DMA FIFO data transfer (e.g. NI CompactRIO, NI R-Series, NI FlexRIO)

Steps to Implement or Execute Code

- Run the RT.vi

Additional Information or References

The test was performed with a CompactRIO-9076 and LabVIEW 2012 and NI-CompactRIO 13.0:

| Method | CPU Usage (%) |

|---|---|

| Blocking | 96 |

| Polling | 19 |

| Polling with Fixed Elements | 92 |

| IRQ | 17 |

| Poll for Size | 11 |

**The code for this example has been edited to meet the new Community Example Style Guidelines. The edited copy is marked with the text 'NIVerified'. Read here for more information about the new Example Guidelines and Community Platform.**

========

CLA and cRIO Fanatic

My writings on LabVIEW Development are at devs.wiresmithtech.com

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

That would be great if U downcast it to LV09! Thank you!

+++ In God we believe, in Trance we Trust +++

[Hungary]

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

really helpful, cheers