Discussions au sujet des autres produits NI

- S'abonner au fil RSS

- Marquer le sujet comme nouveau

- Marquer le sujet comme lu

- Placer ce Sujet en tête de liste pour l'utilisateur actuel

- Ajouter cette question à mes {0}

- S'abonner

- Sourdine

- Page imprimable

FPGA et I/O : comment bien faire ?

le 03-23-2015 10:53 AM

- Marquer comme nouveau

- Ajouter ce message à mes {0}

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner ce Message

- Imprimer

- Signaler un contenu inapproprié

Bonjour,

J'essaie en vain de lire tous mes capteurs en programmation FPGA sur C-RIO 9022 avec un chassis C-RIO 9113.

Je souhaite utiliser le FPGA pour prendre une série de 250 mesures (sur 27 capteurs) sur un pas de temps très court, et ne conserver que la moyenne. Pour cela j'utilise 2 cartes NI-9205.

Je me heurte à 2 méthodes qui ne fonctionnent pas :

(1) Soit je fait une structure séquence de 27 séquences, et dans chacune je fais une boucle de lecture de mon capteur avec un moyennage (Image Erreur_compilation_FPGA.bmp). Dans ce cas je n'arrive pas à compiler, j'ai le message d'erreur suivant : "ERROR:Pack:2310 - Too many comps of type "DSP48E" found to fit this device." J'imagine que la carte FPGA n'est pas dimensionnée pour mon besoin.

(2) Soit je fait une boucle sur chacune de mes entrées, avec dans chacune une boucle de lecture de mon capteur avec un moyennage (image Erreur_refnum_dynamique.bmp). Pour boucler sur mes entrées, je voulais utiliser un tableau de taille fixe avec les refnum de mes entrées. Dans ce cas le vi n'est même pas exécutable, j'ai l'erreur "Fil de liaison : Possibilité de refnum dynamique non supportée pour la cible actuelle".

La seule solution que j'ai trouvé mais qui ne me semble pas très "propre" est de faire 3 VIs FPGA utilisants la méthode (1) avec seulement 9 capteurs chacun. Dans ce cas la compilation fonctionne, et lorsque je souhaite faire la mesure j'appelle successivement mes 3 VIs depuis un Vi en RT.

Voyez vous une solution qui me permettrait de n'avoir qu'un seul VI FPGA qui tourne en boucle, et un Vi RT qui récupère régulièrement les mesures pour les enregistrer ?

Si je ne me trompe pas il n'est pas possible d'avoir plusieurs VI FPGA qui tournent en même temps ?

Merci,

Nicolas

le 03-25-2015 04:09 AM

- Marquer comme nouveau

- Ajouter ce message à mes {0}

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner ce Message

- Imprimer

- Signaler un contenu inapproprié

Bonjour,

Tout d'abord, je pense que vous avez oublié d'attacher vos pièces jointes (et notamment les images).

Ensuite, pour votre premier point, je vous suggère de consulter le forum suivant : Is there an obvious way to prevent an FPGA multiply from using DSPs?

Quant au second point, les deux liens suivants devraient vous aider :

How can i multiplex sensors using the FPGA

Cordialement,

Jérémy C.

NI France

le 03-27-2015 08:16 AM

- Marquer comme nouveau

- Ajouter ce message à mes {0}

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner ce Message

- Imprimer

- Signaler un contenu inapproprié

Bonjour,

J'étais déjà tombé sur ces discussions, mais elles ne me semblent pas très positives.

J'avoue être un peu perdu sur la discussion concernant les DSPs, et la solution proposée concernant les refnums dynamiques semble être celle qui me génère l'erreur DSPs.

Je ne sais pas si j'ai réussi à attacher mes pièces jointes, mais l'idée est de faire autant de boucles que j'ai d'entrées (successivement, pas en parallèle), et une moyenne sur les mesures.

Du coup je n'ai pas besoin que mes boucles tournent en parallèle, je voudrais donc théoriquement réutiliser la même boucle de moyennage, en changeant pour chaque mesure l'entrée et la sortie.

Je ne sais pas si je suis clair, j'espère que les images seront plus parlantes.

Merci

Nicolas

le 05-21-2015 03:10 AM

- Marquer comme nouveau

- Ajouter ce message à mes {0}

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner ce Message

- Imprimer

- Signaler un contenu inapproprié

Bonjour Nicolas

Ce qu'il te faut, c'est utiliser le "IO Sample". Ca permet, avec un seul vi d'avoir accès à toutes les voies du 9205.

Je te join un exemple d'application :

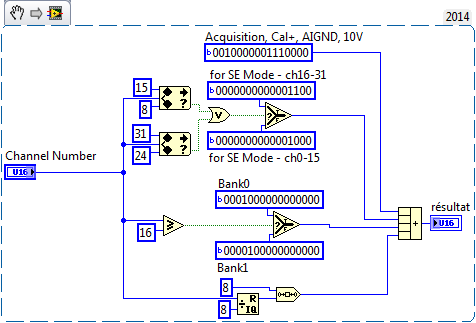

et le codage de la voie (l'insersion du vi ne veux pas fonctionner) :

Attention : la voie à lire est lu 2 coups plus tard, donc il faut prévoir 2 coups à vide pour toi.

le 06-01-2015 05:54 AM

- Marquer comme nouveau

- Ajouter ce message à mes {0}

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner ce Message

- Imprimer

- Signaler un contenu inapproprié

Merci pour cette solution.

Je ne peux malheureusement pas le tester maintenant (le CRIO est utilisé pour des expérimentations), mais je ferai l'essai dès que possible.

Nicolas