Discusiones sobre Productos NI

- Suscribirse a un feed RSS

- Marcar tema como nuevo

- Marcar tema como leído

- Colocar este tema arriba del foro

- Favorito

- Suscribir

- Silenciar

- Página de impresión sencilla

cRIO-9076 NI-9234 FPGA timeout y Overflow.

el 08-27-2015 12:49 PM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Buenas tardes estimados,

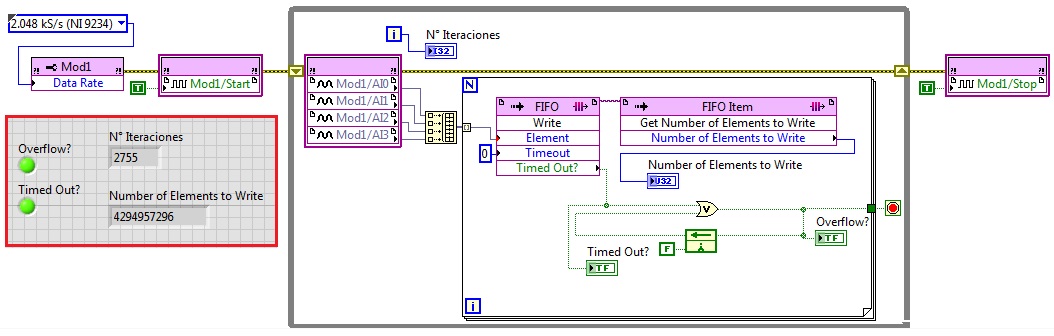

Necesito adquirir datos de un cRIO-9076 y tarjetas de aceleración NI-9234, tenemos el siguiente VI en el FPGA, pero se llena el FIFO constantemente, marca Timeout y Overflow.

Creo que aún no logro entender como trabaja el FIFO, como limpiarlo y descargar los datos antes de que se llene.

FIFO:

Target to Host - DMA

Requested Number of Element: 1023

He buscado varios tutoriales, y no logro solucionar este tema.

Cualquier ayuda es bienvenida, muchas gracias.

Saludos.

Raúl

el 08-31-2015 02:42 PM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Buenas tardes Raúl,

Una buena recomendación para solucionar errores de timeout es utilizar FPGA FIFO methods como clear o flush con el fin de vaciar el FIFO y así evitar la perdida de datos.

Clear (FIFO Method)

http://zone.ni.com/reference/en-XX/help/371599G-01/lvfpga/fifo_clear/

Flush (FIFO Method)

http://zone.ni.com/reference/en-XX/help/371599L-01/lvfpga/fpga_fifo_flush/

Te recomiendo intentar explorar y utilizar estos métodos para controlar situaciones de overflow al trabajar con FIFOs con FPGA.

Saludos!

Daniel C.

el 09-02-2015 03:19 PM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Muchas gracias por responder Danubio, revisaré y aplicaré lo que me mandaste, y comento como me fué.

Saludos.

Raúl