- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What is the max sample clock using the Shielded Single-Ended Flying-Lead Cable

07-10-2015 01:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

What are the max practical limits for the sample clock using the Shielded Single-Ended Flying-Lead Cable?

I am playing with the Labview embedded example "Dynamic Generation and Acquisition Source Synchronou.vi" using the Shielded Single-Ended Flying-Lead Cable and the PXIe-6556.

This example write in the channels 0-7 and read in the channels 7-15.

It also export the sample clock and data active event so we have a "Source Synchronous"

I change the original example to set the input impedance to 50ohm and VH and VL voltatages.Write 3.3V - 0V and read 0.5V 0.3V.

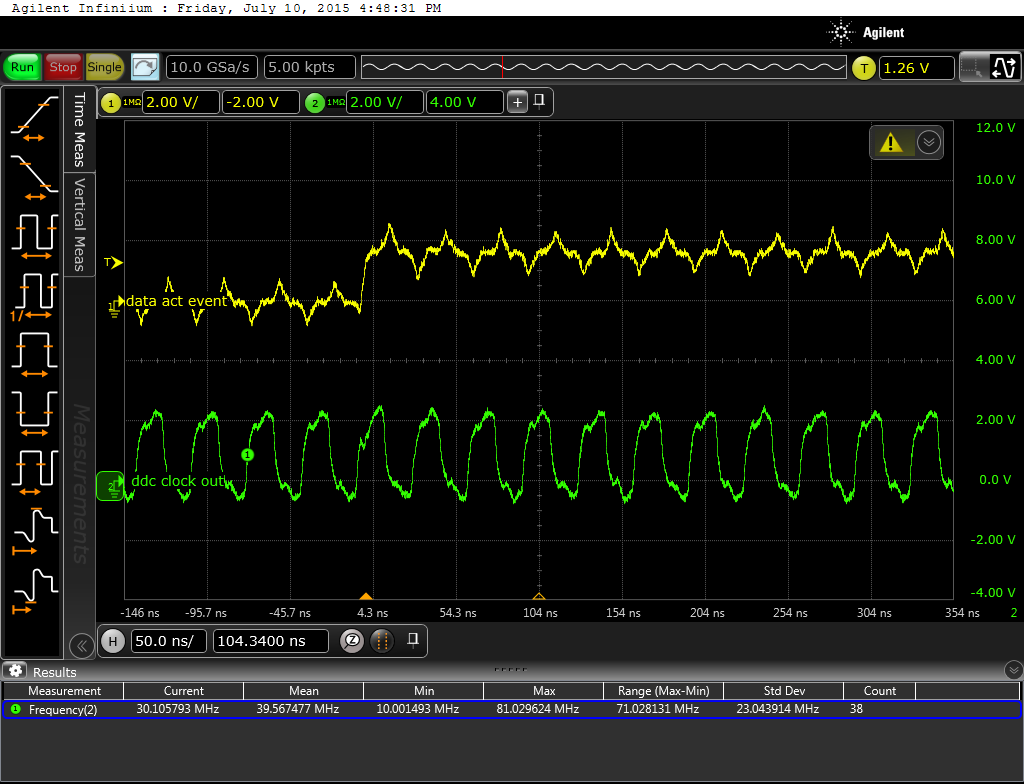

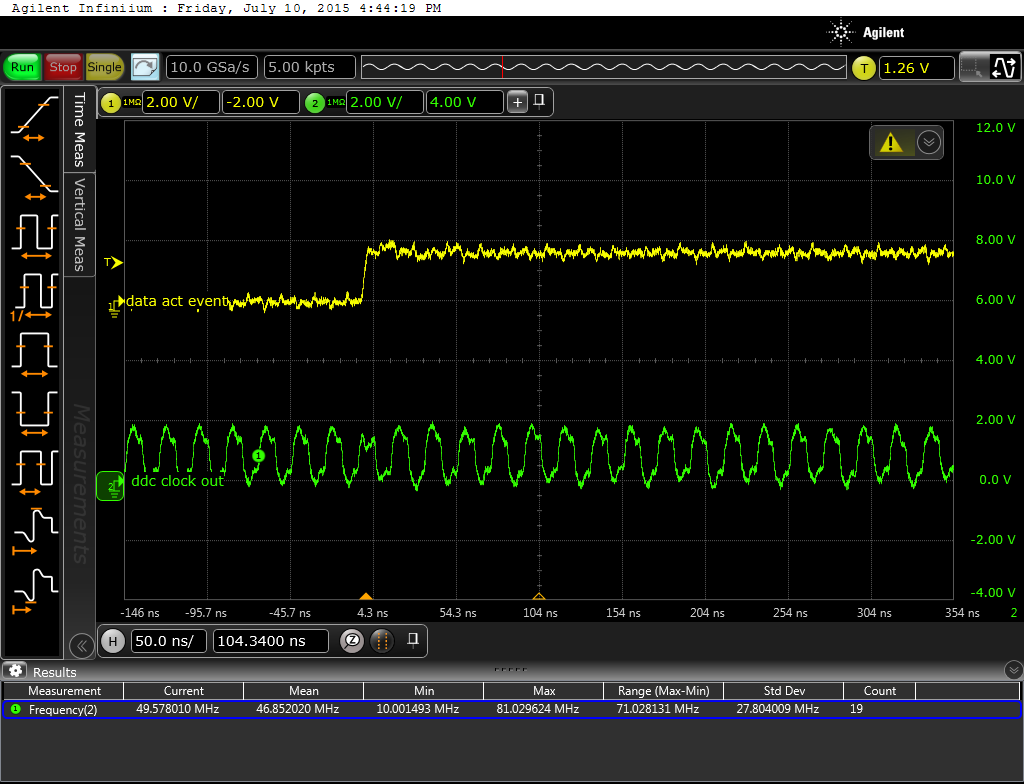

The problem is the signal integrity at higher frequencies. Please see the picture attached.

Sample clock 30MHz

50MHz

70MHz

90MHz

Error: PLL could not phase-lock to the external reference clock.

07-16-2015 03:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello engfpe,

According Hardware manual the Maximum Sample Clock rate is 200 MHz.

http://www.ni.com/datasheet/pdf/en/ds-421

Is not clear for me if your error message was received on LabVIEW or on your Agilent Scope, and I don´t know your Agilent Scopes specifications. Neither I don´t know what exactly you are trying to generate, maybe if yo ucan clarify more your application and your issue I can help you more.

Best regards,

07-21-2015 06:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The error message came from the Labview. The scope is a Agilent MSO9254A Oscilloscope 2.5 GHz.

I am using the example "Dynamic Generation and Acquisition Source Synchronous.vi" to verify which is the max frequency I can send the digital signals in the source synchronous configuration.

There is any circuit I just connect input and outputs directly. In the scope we can see that the "ddc clock out" signal" is degrading when I increase the frequency.