- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Timing gap in onboard looping in the PCI 6543

06-28-2015 02:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I want to do onboard looping in the PCI 6543. Is there any timing gap between the loops? Within each loop, the board updates data with each clock strobe. After finishing the last sample of a loop, will it move on to the first sample of a new loop immediately with the next clock strobe? If not, how long does it take to transit from one loop to the next?

06-29-2015 11:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Wait,

I'm not familiar with the 6543, can you confirm what hardware it is that you're using? Is there any way it might be the 6534?

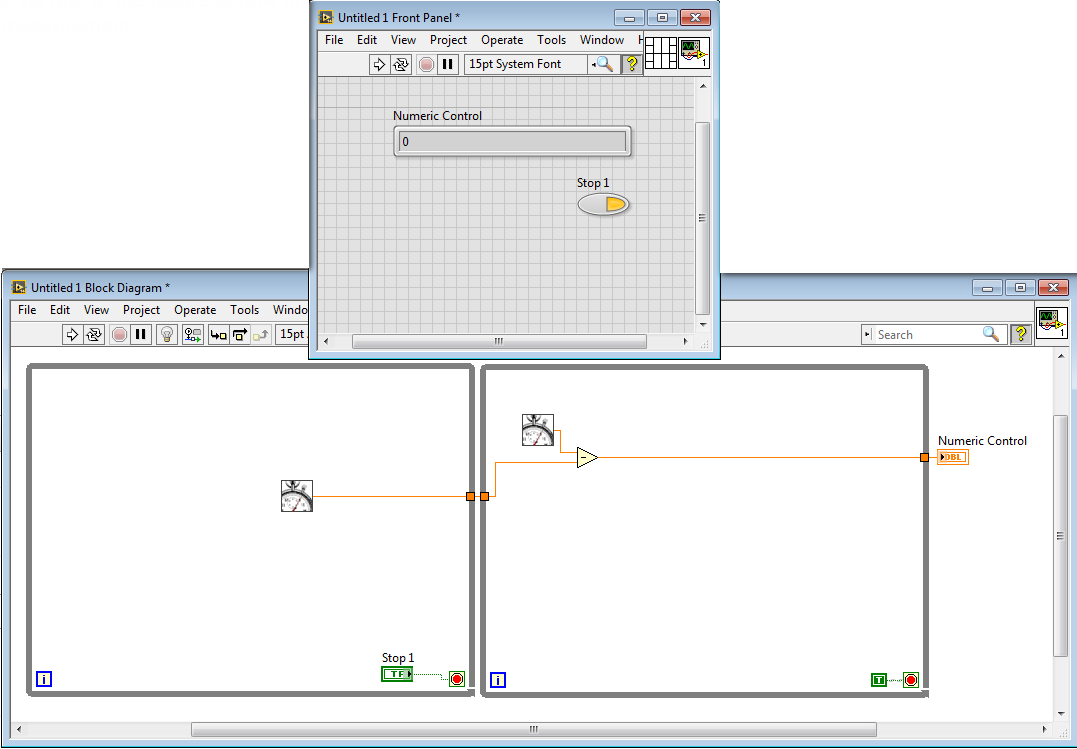

It sounds like your main question is how many clock cycles would occur between the end of one while/for loop and the start of another while/for loop. Is that correct? Could you provide a screenshot of your code so that I might have a better idea of what it looks like?

Technical Marketing Specialist

National Instruments

06-29-2015 01:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks, Ty. I am really using PCI 6534 not 6543. Your paraphase is essentially correct. I have a screenshot of the code written by my colleague in NI-DAQ. When I try to upgrade the code to DAQmx, I come across this question.

06-30-2015 10:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Unfortunately, there's no real way to tell how long that time is going to be due to the nature of how operating systems handle tasks. However, it's going to be extremely fast. Even with our most precise time measurement, it says that there is 0 time between the two loops.

Do you have any concern about the time between loops, or what is the root reason that you're wondering about this?

Technical Marketing Specialist

National Instruments

06-30-2015 01:41 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The concern is that we observed some phase jitter between 60 Hz signal from the power line and pulses generated by the PCI 6534 clocked by GPS. This can be a result of that the 60 Hz signal from the power line itself is noisy or that the PCI 6524 itself is not well clocked.

Maybe I misunderstand what you said. The advantage of the onboard memory is that the PCI 6534 does not have to receive data from the computer in order to generate the next loop of samples. So I would think the time gap is independant of the computer.

If my clock frequency is 1 MHz, do you mean the time gap is less than 1 us?

07-01-2015 11:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Wait,

I haven't been able to verify this for certain, but according to the white paper associated with this onboard outputting (http://www.ni.com/white-paper/3631/en/), :"Speed is independent of the system, and can be sustained at 20 MHz." Therefore, I believe that there should be no discontinuity between the end of the buffer and start of the next iteration, and you are correct in that there is no association with the computer.

Applications Engineering

National Instruments