- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PXI-6552 generation and acquisition

06-26-2012 10:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am working on my ADC verification with HSDIO. I am new to PXI-6552 and I really need advice.

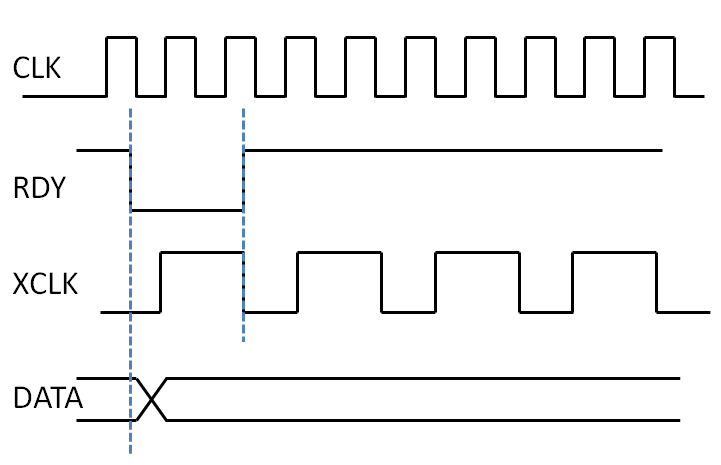

The picture below is the timing diagram of ADC.

Basically, CLK is a continuous signal. I have to wait RDY going from High to Low then I can send XCLK signal into ADC. I also need get one bit data from DATA pin when XCLK on the rising edge.

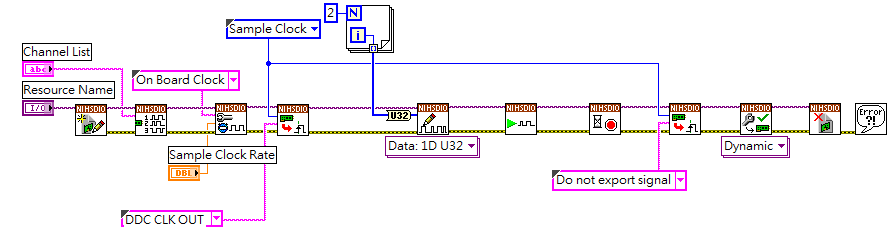

I knew how to generate two different frequencies (CLK = 4MHz, XCLK = 800kHz) to control my DUT. I set the clock rate to 8MHz, therefore, digital pin0 will be 0101010101 and digital pin1 will be 0000011111.

Though, I still have a couple of questions about generation and acquisition.

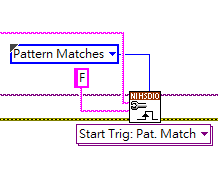

1) I used Configure Trigger VI to capture falling edge of RDY, is there a easy way to detect rising or falling edge?

2) Once generation session starts, two digital pins keep sending signals to ADC. How to disable pin1 and make pin0 work at the same time and enable pin1 later? Is it possible to do it without using Abort VI?

3) Because the timing is very critical, how to immediately acquire data from DATA pin while XCLK going high?

It would be much appreciated if anyone can share some thoughts to me....

Thanks,

Shou

07-02-2012 04:42 AM - edited 07-02-2012 04:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Nisml

Thanks for using National Instruments discussion forum.

I looked into your program.

You are writing data (30 samples) on Ch0(pin0?) and

reading Ch2(pin1?).

Is that how you get two channel outputs.

In response to your querries

1) Digital edge trigger can be used with source of trigger being RDY.

2) Please confirm the pin0 and pin1 output terminals.I wonder you won't have much options without aborting the VI.

If you need to use one line at a time, you may specify one line (say line 3) for output and multiplexing between

pin0 and pin1 as per requirements.

3) You can do acquisition using XCLK through cklin terminal.

please confirm about above points.

regards,

Muhammad

07-04-2012 08:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Muhammad,

I came up some ideas last Friday. Please correct me if I'm wrong.

1) I found an example like yours. It's just what I need!!!!!

2) I was wondering that it's no way to implement what I tried to do. So I exported the CLK pin (4MHz) to DDC CLK OUT on CB-2162 (no more pin0) and control pin1 only.

3) sorry, I didn't understand what you mean "You can do acquisition using XCLK through cklin terminal". Could you please specify more details?

Thanks,

Shou

07-06-2012 12:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Shou

Great to see that you could find a workaround by exporting sample clock and using digital edge trigger.

About your query no.3, as you want to acquire data with every rising edge of XCLK, I thought its better to do data acquisition using external clock(XCLK) at clkin.

you may find an example program in NI Sample finder. e.g. NI-HSDIO (High-Speed I/O)> Dynamic Acquisition > Dynamic Acquisition with External Sample Clock.vi

regards,

Muhammad