- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I2C Digital Waveform (IDW)

08-16-2010 04:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Raj -

"SCL held low until data is processed" sounds like clock stretching. This is a feature defined in the I2C specification wherein a slave device forces the bus clock not to toggle until it is ready. Unfortunately, there's no way to allow clock stretching with IDW because one of the core design assumptions of this library is that the clock is generated and controlled by the bus master device (NI HSDIO card).

To implement an I2C master that allows clock stretching, I recommend using an R-series module with LabVIEW FPGA.

You might be able to define a worst-case pause length and manually insert it at the end of your messages, so the HSDIO card will wait while the message is being processed by the slave. This depends on whether the slave needs the next byte immediately after it is done processing the current one.

Staff Systems Engineer

National Instruments

09-07-2010 04:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes, it was clock stretching. I was able to blank and then insert delays to make it work. It could be fragile but should be testable that it will work in all cases.

I don't see a PXIe version of 6551. Is there a PXIe HSDIO card that is supposed to work with the IDW library?

09-07-2010 04:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Raj -

You're looking for the PXIe-6547 or PXIe-6548.

Staff Systems Engineer

National Instruments

10-19-2010 05:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ppl

Quick question. Did anyone try to make i2c work on a cRIO, using fx. 9401 DIO module??

10-19-2010 09:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi soeren -

This thread is only for discussing IDW-based I2C solutions for DAQ and HSDIO products. Please discuss cRIO hardware in the Real-Time Measurement and Control hardware forum, or general LVFPGA questions in the LabVIEW software forum.

Staff Systems Engineer

National Instruments

10-19-2010 09:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

An FPGA-based example for I2C is posted in Developer Zone here.

A turnkey SPI/I2C module for cRIO is available from TangentBlue

03-10-2011 08:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi David,

I have to control a I2C device for which I recently ordered NI USB-8451 which provide a convenient USB to 2 wire interface. Do you think I can use the I2C Digital Waveform (IDW) library to develop a Labview based programme for my application? I am basically concerned with generating the appropriate SCL and SDL signals similar to the ones shown IWD examples. Kindly give you feedback and detailed comments as I am completely new to this. Eagerly looking forward to hear from you.

-Ravi

03-10-2011 09:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ravi -

The 8451 is a native I2C I/O device that plugs into a USB port. It comes with a unique driver whose API allows you to configure all the parameters of an I2C communication and manipulate it to send and receive data through the protocol. As such, there is no need to use the IDW library with it. As explained in the IDW article linked from the first post in this thread, that library was written to work with simple digital vector devices that use the NI-HSDIO and NI-DAQmx drivers.

If you need support using your 8451, you can find lots of questions and answers all over the forum by searching for the string "8451": http://forums.ni.com/t5/forums/searchpage/tab/message?q=8451#message-list If you have a question that hasn't yet been answered, I recommend posting in the "Digital I/O" forum.

Staff Systems Engineer

National Instruments

05-11-2011 02:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@David S. wrote:

Hi pgo -

No, as explained in this thread earlier, you can't use IDW with any device that does not support per-cycle tristate. No DAQ device has this feature as of today.

It is possible to create a single-master, single-slave interconnection using active-driven signals from the master, but you still need pullup resistors on the bus for the slave's open-drain I/O. With this setup, you won't be able to hear what the slave is saying any time the master is driving a '1' onto the SDA line. You can create such a solution by hacking the IDW to drive '1' instead of 'Z': a simple find-and-replace on all IDW VIs should accomplish this. However, since it's a modification of the published code, I won't be able to help you troubleshoot the implementation.

I am planning to implement I2C using the PXIe-6363 DAQ. It's my understanding this device does not support per-cycle tristate. Is that a correct assumption?

Since this will be a single-master, single-slave implementation, I will modify the IDW to drive '1' instead of 'Z'. Any other tweaks/modifications required?

Thanks!

Gary

03-21-2012 05:06 AM - edited 03-21-2012 05:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

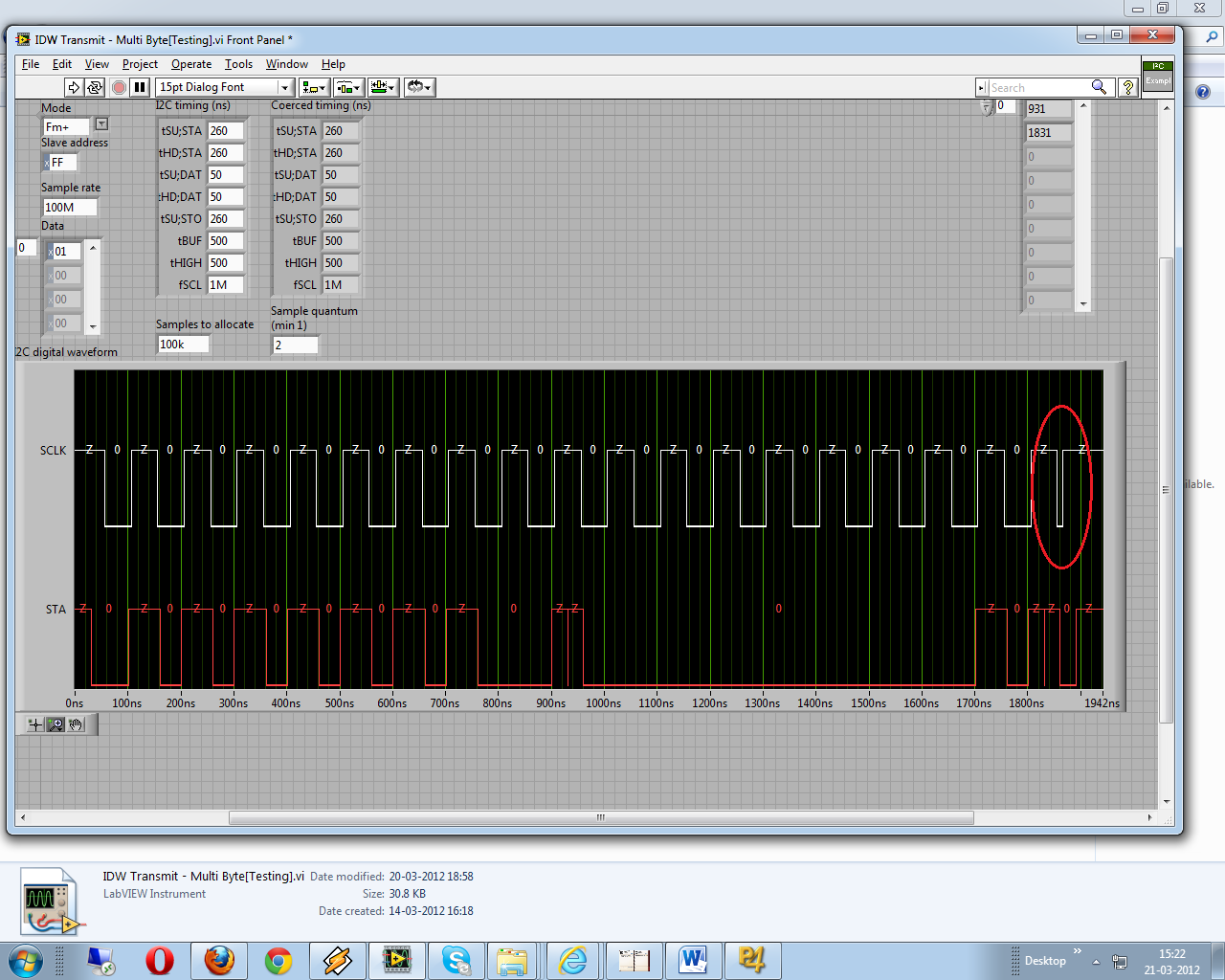

For some combination of the input the clock is making irregular transition before generating the STOP condition, please let me know how to change it. I am operating in Fm+ mode.