- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CLD Prep Boiler Practice Test Critique

03-28-2016 08:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello All,

This is my second attempt at a CLD practice test. This time it's the Boiler example. Once again, any constructive feedback would be appreciated. I think that the only functional requirement that I missed was for the boiler to begin its purge any time the flow is below 10% or above 75%. I also realize now that I left the pre-defined type-defs with their original icons and did not add documentation to those. But this is where I ended up after 4 hours.

The zipped project is for LV 2014.

Thanks to all.

Dan

03-29-2016 07:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Overall - looks like a pretty good solution and the code itself is pretty well documented.

Some things I noticed:

- There are quite a few unnecessary wire bends in places (including some backwards wires!) and some overlapping constants. This might just be personal preference, but I always try to have the wires of constants coming out of the right-hand side of the constant. Try to give yourself a bit of time at the end to 'tidy up'.

- As you pointed out, don't forget to document type definitions (icon + description)

- Error handling - you have the error on a shift register which means that if an error occurs at any stage of the application, it will stay in that shift register indefinitely (and any subsequent VIs will fail to execute due to normal error handling. I don't know if there were any requirements for error handling in the scenario (e.g. stop on error, go to an error state case)? Make sure you document your design on error handling.

- Your 'enable' case of the Control Enable-Disable SubVI has different error handling to the other cases. If that was deliberate, you should document it. If there was an error, you would get the automatic error handling popup

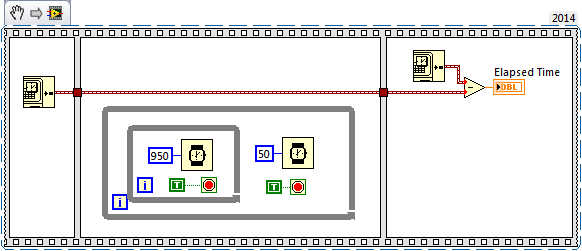

- In your 'purge incomplete' case, I think you have misunderstood how the Wait (ms) function works when it is nested in a loop. You have a 950ms wait inside the case, and then a 50ms loop for execution timing. This doesn't 'add up' to a 1 second wait. The 50ms wait starts when the while loop starts, so it has already elapsed by the time the 950ms wait finishes on the inner case - so the loop timing is 950ms instead of 1 second. Check out this simple example benchmark:

Hope that helps - good luck with the exam!

03-29-2016 07:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for the excellent feedback. I'll be sure to take it into account on future attempts.

Yes, I needed more "tidy-up" time than I gave myself. It's just so hard for me to move on to tidying-up when I know there is still a functional issue. I have to work on that because I know style can count about as much as function in the CLD.

I completely missed that the error cluster in the Enable case of the Control Enable-Disable sub vi was incompletely wired. That would've been a quick fix if I'd caught it.

Your pointer on the wait function is helpful. I saw that my log entries were coming in at 950 ms, but didn't see the root of the problem.

Sincere thanks again.

Dan