- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

fpga

02-28-2013 06:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

I am learning on ELVIS II the basics of FPGA. I have been asked to code a state machine where from idle state, pressing button 0, should go into a count-up state (0-99) and when reach 99, move to next step counting down 99-0, then return to idle. At any moment of the count up state, if user press button 1, count up should be aborted and return to idle state. As a note, both counting up and down should display the number on the FPGA segment display.

Now, I am using for loop to count 0-99 and 99-0, but happen that once in for loop, we cant make the button 1 to be read during the counting. Looks like for loops takes over the entire code until after it finishes. May I am using a wrong approach, so please support into learn the correct technique.

Thanks

David

03-05-2013 02:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

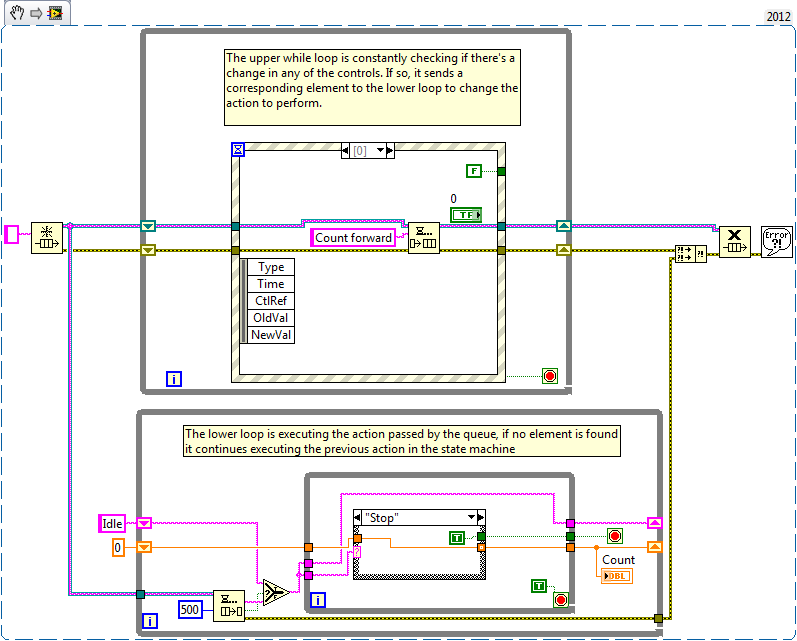

To solve your problem you can use another type of architecture, in this case event consumer and producer loop. I'm adding a simple example program of how it works.

I hope this is useful!

National Instruments

ELP Support Engineer

www.ni.com/soporte

03-21-2013 09:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, I was double checking the post, and I noticed that the example I gave you will not work with FPGA. The following links give you some examples of how can you make your application, the first one using directly Xilinx ISE Tools, and the second one with LabVIEW.

Building a Finite State Machine for the NI DE FPGA Board

http://www.ni.com/white-paper/8860/en

State Machines for FPGA-Based Controllers

https://decibel.ni.com/content/docs/DOC-6375

Regards,

National Instruments

ELP Support Engineer

www.ni.com/soporte