- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MyRIO Real-Time Target Timing Error

02-05-2015 10:56 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

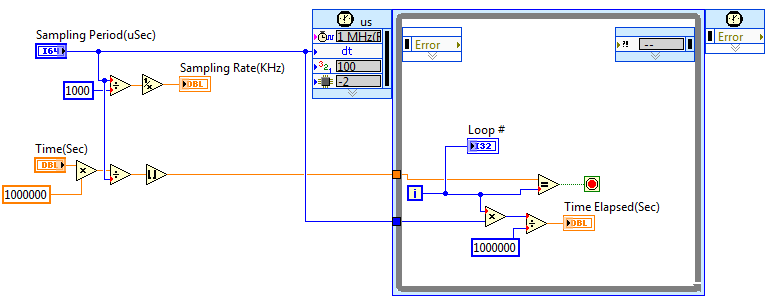

On myrio real-time target, I created a VI with a timed loop with 1MHz clock. The dt value is given by my input. Inside the timed loop, there is basically nothing. I tried a few different dt values. When dt >= 100us (i.e. the rate is 10KHz or less), timing is correct. When dt <= 100us (i.e. the rate is greater than 10KHz), the timing will be so wrong. One case with error would be dt = 10us (rate = 100KHz), the elapsed time goes quite slower than actual time clock.

Here is my block diagram.

Can someone help me debug this issue?

Thanks a lot.

02-09-2015 10:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello geliang87,

The reason you are experiencing this behavior is due to the fact that the period you are assigning to the timed loop is close to the duration of the iteration (you can benchmark this by using the iteration duration node inside the timed loop), which makes the iteration finish after the period time finishes. This makes the next iteration start on the third period rather than the second period.

Regards

02-09-2015 11:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jose,

Got your point. Thank you.

My application requires a high sampling rate (up to 100KHz). I guess I should program on fpga instead of rt target.

Regards,

Liang