From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

06-16-2017 07:31 AM

Hello,

I am studying the performance of the 802.11 ac standard using NI USRP 2954R. For this, I need the 80 MHz bandwidth. As the white paper states, this is possible:

Note that in the FPGA bitfiles included in the Application Framework project template, 80 MHz bandwidth support is disabled, so only options 1 to 3 are applicable. To enable options 4 and 5, the bitfile must be rebuilt with the 80 MHz Boolean enabled in the supported bandwidth cluster.

I have done this, and created the cases in the VIs for the 80 MHz bandwidth. However, I can't see results, the throughput being 0, and only 1 packet start detected.

What am I missing?

Any help is greatly appreciated.

Thanks!

Cristian

06-19-2017 06:20 PM

Hi Cristian,

It is my understanding that you also need to redesign the bit processing modules of TX and RX to work in parallel. Besides that, it seems like you got the right thing. That is a super basic version of the answer. I am working to see if I can provide a more thorough answer.

Cheers,

Michael

06-23-2017 09:03 AM

Hi Michael,

Thank you for your time. I could not find out (yet) what modifications should I do in the bit processing modules nor in other modules since it seems that the cases are already made for the 80 MHz bandwidth. What I found out was that in the Power Measurement module, in the FIR Low Pass Filter.gcdl the case for 80 MHz was not made, but I am not sure whether this change is enough.

I find this very intriguing...any help is appreciated..

Thanks in advance!

Regards,

Cristian

06-27-2017 04:02 PM

Hi Cristian,

I wanted to let you know that I am still working on this. It may take some time to compile the information together.

Cheers,

Michael

07-07-2017 10:47 AM

Here is a long awaited answer.

To support the 802.11ac 80 MHz Subcarrier Format, let us summarize the required modifications into two parts.

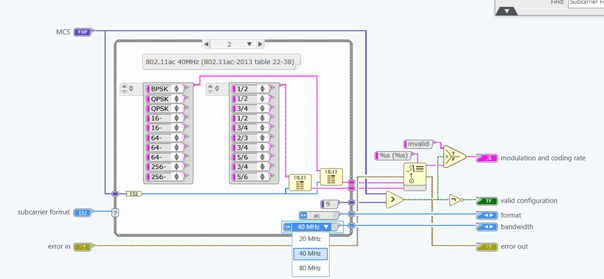

Part 1: Enabling the 802.11ac (80 MHz) Subcarrier Format

To enable the 802.11ac 80 MHz Subcarrier Format in the FPGA, you need to do the following:

Part 2: Factors to consider, when using 802.11ac (80 MHz) with USRP-2953R

The 802.11 Application Framework is ready to support 80 MHz BW. However, the 802.11ac (80 MHz) format has data rates that exceed the existing FPGA clock rate (250MHz).

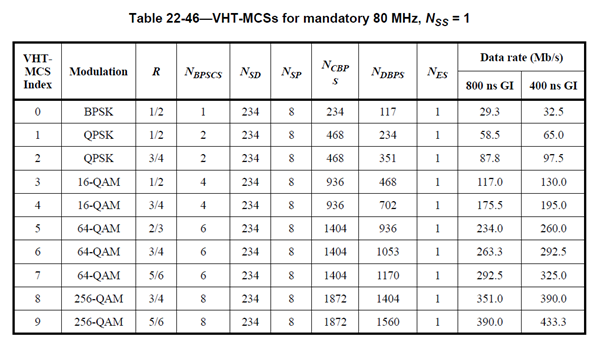

If we only apply the changes from Part 1, "Enabling the 802.11ac (80 MHz) Subcarrier Format" post, then you should be able to generate and receive 80 MHz BW signals with modulation coding schemes (MCS) <= 2. The clock rate of RX and TX baseband loops is 250 MHz. That means that the maximum bit rate that can be achieved theoretically is 250 Mbit/s. More practically, the clock rate of the FPGA is around 230 Mbps. For 802.11ac : 80 MHz : MCS 5 : GI 800ns, the data rate is 234 Mbps, which is above the practical limit of the FPGA. However, the biggest bottleneck is the number of bits processed per unit of time. To support the high date rates of 80 MHz bandwidth, the bit processing module of TX and RX should be redesigned to work in parallel.

To support higher MCS levels in the TX loop TX bit processing must be switched from a serial operation to parallel such that instead of producing 1 bit at a time we are producing multiple bits. (at least two bits at every clock cycle) In the image below, the highlighted chain (in red) is the one that would need to be improved to work on at least 2 samples per cycle. Complexity wise the Serializer, Scrambler, QAM mapper and Encoder are simpler to complete. The Puncturer and Interleaver could be more complex. On the receiver side the Viterbi Decoder is most likely the most complex block.

Subsequently the symbol generation also needs to be switched to support multiple bits in one clock cycle.

Note: This 80 MHz implementation has not been tested with USRP-RIO and more modification may be needed to be done to have it work.

Cheers,

Michael

07-07-2017 12:57 PM

I should also note that the above is not an official statement of any type and may change in the future.

07-15-2017 06:53 AM

Hi Michael,

Thank you so much for this answer! I will tell you my results as soon as I get to work again with the USRPs.

Thank you again!

Cheers,

Cristian

11-29-2018 05:57 PM

Can you please elaborate on compiling the lvbit file, am using 802.11 application framework 2.1 and couldn't find step 1 and 2 of your solution. I was not able to find the bandwidth selection, and can also please share how to build, I found the remaining steps in your answer in the suite

your answer will greatly help, as am struggling for awhile to get this done

12-19-2018 02:45 PM

Are these instructions still valid? It appears that in the time since this detailed set of instructions were originally posted, the code has gone through changes and no longer has the supported bandwidths configuration item. Is this the case?

12-19-2018 03:42 PM

I have not gotten a chance to look at what it would take in newer versions and it is not in my priority list at the moment. Since this wasn't an official document or guide I wouldn't wait on it to be updated for the newer versions. I'm sorry for the inconvenience.